Debug

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

11-21

ID013010

Non-Confidential, Unrestricted Access

11.4.9

Debug State Cache Control Register

The DSCCR controls the L1 cache behavior when the processor is in debug state.

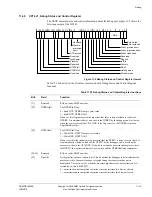

Figure 11-8 shows the bit arrangement of the DSCCR.

Figure 11-8 Debug State Cache Control Register format

For information on the usage model of the DSCCR register, see

Cache debug

on page 11-50.

Table 11-14 shows how the bit values correspond with the Debug State Cache Control Register

functions.

11.4.10 Instruction Transfer Register

The ITR enables the external debugger to feed instructions into the processor for execution

while in debug state. The ITR is a write-only register. Reads from the ITR return an

Unpredictable value.

The Instruction Transfer Register, bits [31:0] contain the ARM instruction for the processor to

execute while in debug state. The reset value of this register is Unpredictable.

Note

Writes to the ITR when the processor is not in debug state or the DSCR[13] execute instruction

enable bit is cleared are Unpredictable. When an instruction is issued to the processor, the debug

unit prevents the next instruction from being issued until the DSCR[25] instruction complete bit

is set.

31

2 1

31

0

Not write-through

Reserved

3

Instruction cache line-fill

Data cache line-fill

Table 11-14 Debug State Cache Control Register functions

Bits

Field

Reset

value

Description

[31:3]

Reserved

0

Reserved. Do not modify on writes. On reads, the value returns zero.

[2]

nWT

0

Not write-through:

1 = normal operation of regions marked as write-back in debug state

0 = force write-through behavior for regions marked as write-back in debug state, this is

the reset value.

[1]

nIL

0

Instruction cache line-fill:

1 = normal operation of L1 instruction cache in debug state

0 = L1 instruction cache line-fills disabled in debug state, this is the reset value.

[0]

nDL

0

Data cache line-fill:

1 = normal operation of L1 data cache in debug state

0 = L1 data cache line-fills disabled in debug state, this is the reset value.