FPU Programmer’s Model

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

12-6

ID013010

Non-Confidential, Unrestricted Access

12.3.2

Floating-Point Status and Control Register, FPSCR

FPSCR is a read/write register that can be accessed in both Privileged and nonprivileged modes.

All bits described as DNM in Figure 12-3 are reserved for future expansion. These bits must be

initialized to zeros. To ensure that these bits are not modified, any code other than initialization

code must use read-modify-write techniques when writing to FPSCR. Failure to observe this

rule can cause Unpredictable results in future systems.

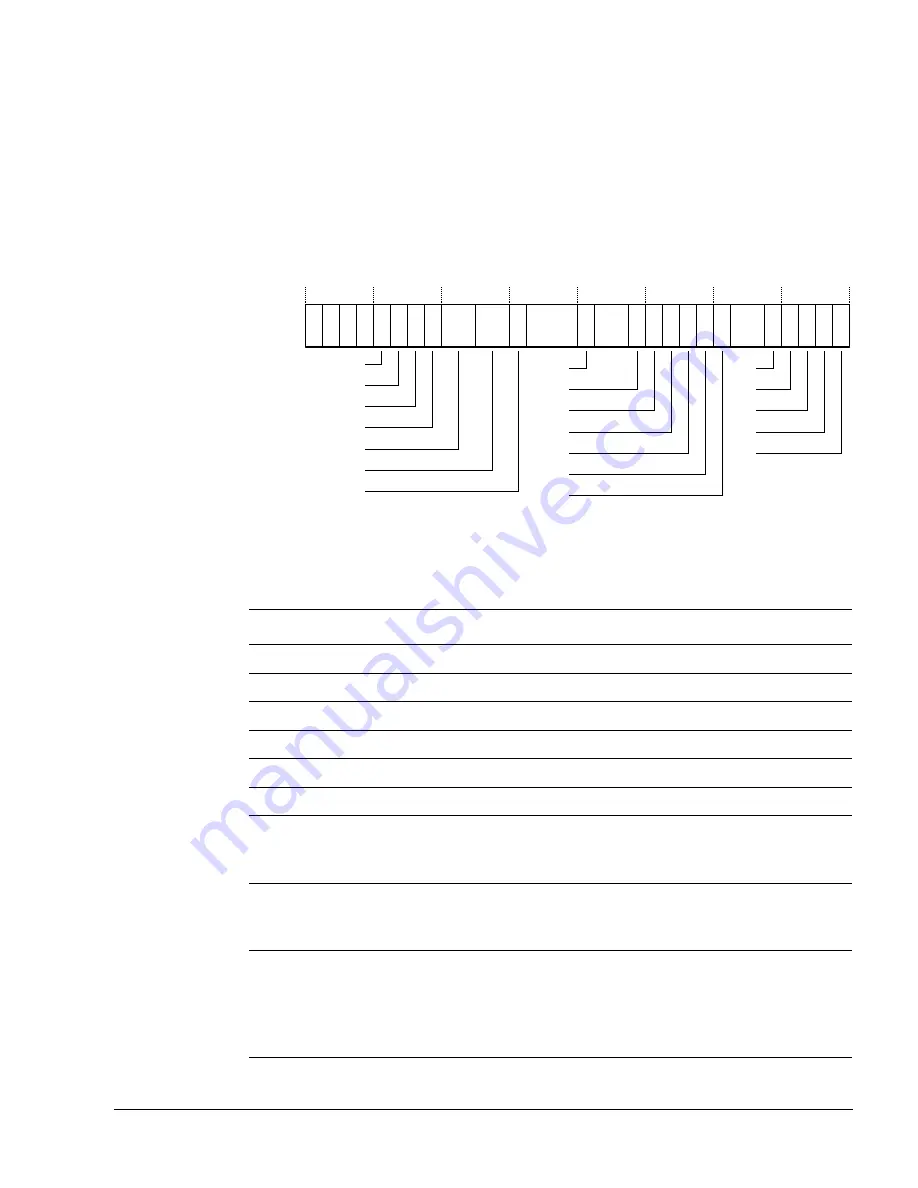

Figure 12-3 shows the bit arrangement of the FPSCR Register.

Figure 12-3 Floating-Point Status and Control Register format

Table 12-4 shows how the bit values correspond with the FPSCR Register functions.

IXC

IDC

DNM

DZE

IOE

UFE

OFE

DNM

IXE

IDE

LEN

DNM

N Z C V

UFC

OFC

DZC

IOC

QC

RMODE

STRIDE

DN

FZ

DNM

31 30 29 28 27 26 25 24 23 22 21 20 19 18

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Table 12-4 FPSCR Register bit functions

Bits

Field

Function

[31]

N

Set if comparison produces a

less than

result, resets to zero

[30]

Z

Set if comparison produces an

equal

result, resets to zero

[29]

C

Set if comparison produces an

equal

,

greater than

, or

unordered

result, resets to zero

[28]

V

Set if comparison produces an

unordered

result, resets to zero

[27]

QC

Do Not Modify

(DNM)/

Read As Zero

(RAZ)

[26]

DNM

DNM

[25]

DN

Default NaN mode enable bit:

0 = default NaN mode disabled, this is the reset value

1 = default NaN mode enabled.

[24]

FZ

Flush-to-zero mode enable bit:

0 = flush-to-zero mode disabled, this is the reset value

1 = flush-to-zero mode enabled.

[23:22]

RMODE

Rounding mode control field:

b00 = round to nearest (RN) mode, this is the reset value

b01 = round towards plus infinity (RP) mode

b10 = round towards minus infinity (RM) mode

b11 = round towards zero (RZ) mode.

[21:20]

STRIDE

Indicates the vector stride, reset value is

0x0