Integration Test Registers

ARM DDI 0363E

Copyright © 2009 ARM Limited. All rights reserved.

13-5

ID013010

Non-Confidential, Unrestricted Access

13.4

Processor integration testing

This section describes the behavior and use of the Integration Test Registers that are in the

processor. It also describes the Integration Mode Control Register that controls the use of the

Integration Test Registers. For more information about the ITCTRL see the

ARM Architecture

Reference Manual

.

If you want to access these registers you must first set bit [0] of the Integration Mode Control

Register to 1.

•

You can use the write-only Integration Test Registers to set the outputs of some of the

processor signals. Table 13-2 shows the signals that you can write in this way.

•

You can use the read-only Integration Test Registers to read the state of some of the

processor inputs. Table 13-3 on page 13-6 shows the signals that you can read in this way.

There are Integration Test Registers that you can use in conjunction with ETM-R4 integration.

For more information see the

ETM-R4 Technical Reference Manual

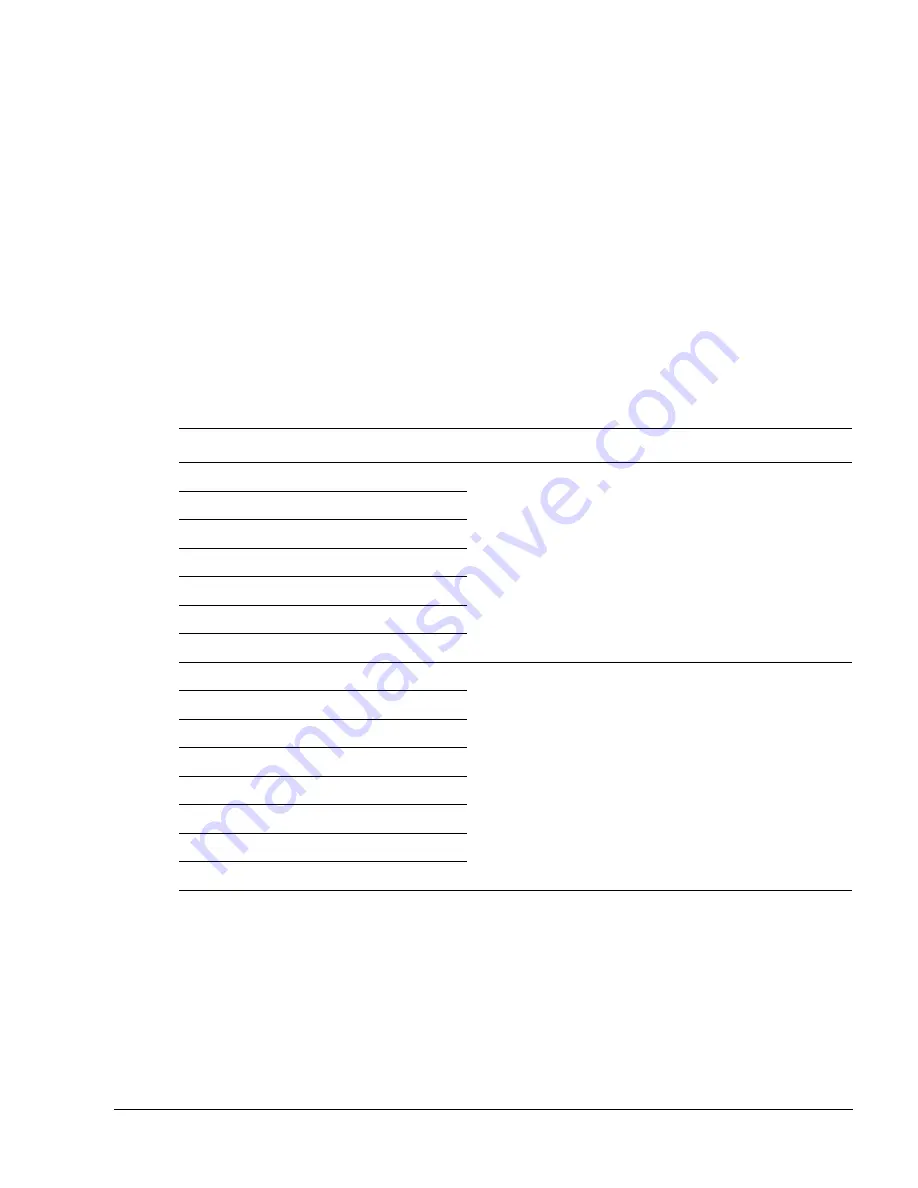

Table 13-2 Output signals that can be controlled by the Integration Test Registers

Signal

Register

Bit

Register description

DBGRESTARTED

ITMISCOUT

[9]

See

ITMISCOUT Register (Miscellaneous Outputs)

on page 13-8

DBGTRIGGER

ITMISCOUT

[8]

ETMWFIPENDING

ITMISCOUT

[5]

nPMUIRQ

ITMISCOUT

[4]

COMMTX

ITMISCOUT

[2]

COMMRX

ITMISCOUT

[1]

DBGACK

ITMISCOUT

[0]

EVNTBUS[46]

ITETMIF

[14]

See

ITETMIF Register (ETM interface)

on page 13-7

EVNTBUS[28, 0]

ITETMIF

[13:12]

ETMCID[31, 0]

ITETMIF

[11:10]

ETMDA[31, 0]

ITETMIF

[7:6]

ETMDCTL[11, 0]

ITETMIF

[5:4]

ETMDD[63, 0]

ITETMIF

[9:8]

ETMIA[31, 1]

ITETMIF

[3:2]

ETMICTL[13, 0]

ITETMIF

[1:0]