The target:

• Writes data to

SWDIO

on the rising edge of

SWCLK

.

• Reads data from

SWDIO

on the rising edge of

SWCLK

.

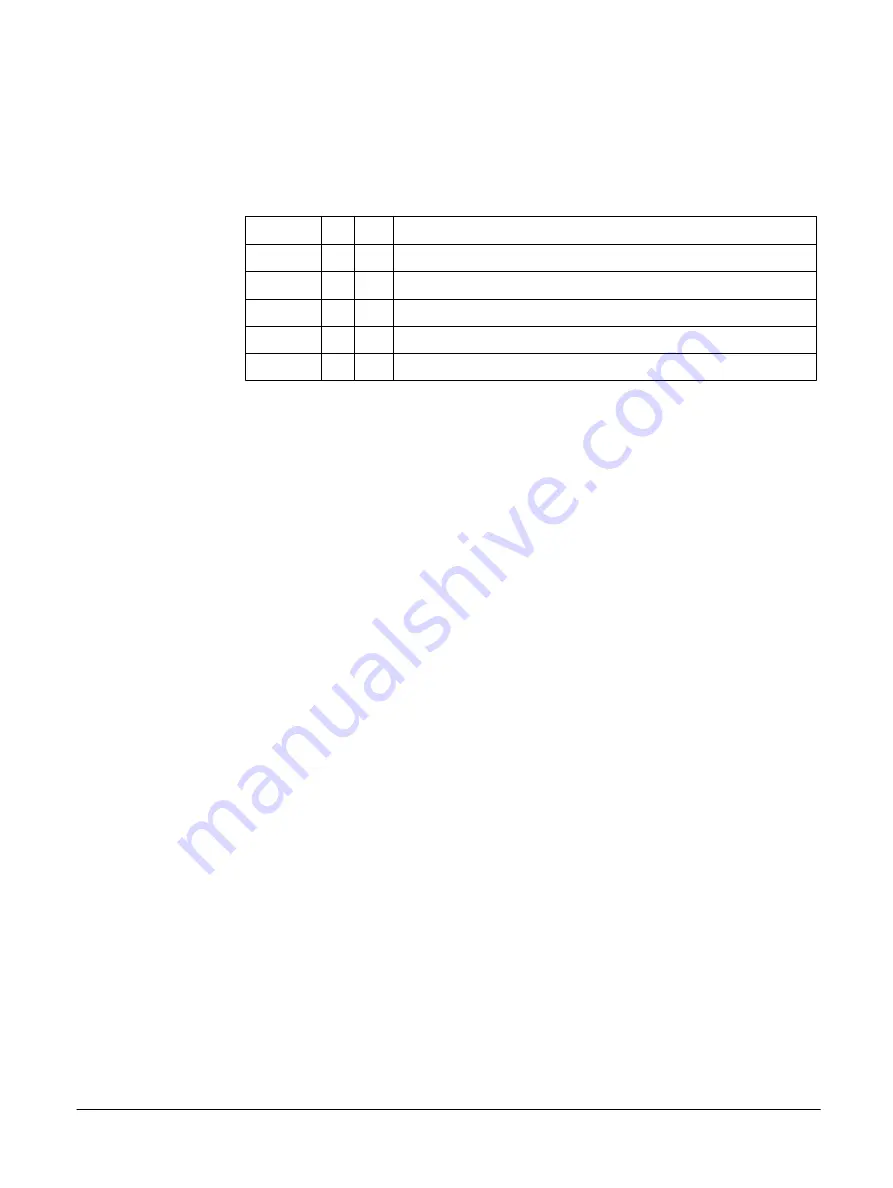

The following table shows the timing requirements for SWD:

Table 1-2 SWD timing requirements

Parameter Min Max Description

T[high]

4ns 50ms

SWCLK

HIGH

period.

T[low]

4ns 50ms

SWCLK

LOW

period.

T[os]

-1ns 1ns

SWDIO

output skew to falling edge

SWCLK

.

T[is]

4ns -

Input setup time that is required between

SWDIO

and rising edge

SWCLK

.

T[ih]

1ns -

Input hold time that is required between

SWDIO

and rising edge

SWCLK

.

1 Debug and trace interface

1.5 Serial Wire Debug (SWD) signals

101714_0100_02_en

Copyright © 2019 Arm Limited or its affiliates. All rights reserved.

1-23

Non-Confidential