1.3

Reset signals

Arm debug units have the ability to control two reset signals on the target:

nSRST

and

nTRST

.

System Reset (nSRST)

The system reset signal, sometimes known as

nRESET

or

HRESET

, is an input to the target which

performs a warm boot of the core (or cores) and other devices in the target system. It is often asserted by

one or more of these conditions:

• Power On Reset (POR)

• Manual push-button reset

• Remote reset from a debug unit

• Watchdog reset

When no debug unit is connected, unintended resets can occur. To avoid unintended resets, the

nSRST

signal must be pulled to its inactive logic level on the target.

By default, the

nSRST

signal has a logic level of active

LOW

. To avoid unintended resets, pull the

nSRST

signal

HIGH

.

The polarity of the

nSRST

signal is configurable in Arm Development Studio.

TAP Reset (nTRST)

The TAP reset signal initializes the Test Access Port, debug logic, and boundary scan cells in the target

device.

When no debug unit is connected, unintended resets can occur. To avoid unintended resets, the

nTRST

signal must be pulled to its inactive logic level on the target.

By default, the nTRST signal has a logic level of active

LOW

. To avoid unintended resets, pull the nTRST

signal

HIGH

.

The polarity of the

nTRST

signal is configurable in Arm Development Studio.

Note

Arm strongly recommends that the

nSRST

and

nTRST

signals are separately available on the JTAG

connector. If the

nSRST

and

nTRST

signals are linked together, resetting the system also resets the TAP

controller, which means:

• Depending on your target, it might not be possible to debug a system from reset because any

breakpoints previously set might be lost.

• You might need to restart the debug session because the JTAG interface might not recover when the

TAP controller state is changed.

It is expected that the assertion of the

nSRST

line by the DSTREAM-PT system will cause a warm reset

of the target system. If the

nSRST

line triggers a full, Power On Reset (POR), then the debug connection

might be lost.

With regards to the reset signals output from the DSTREAM-PT system, the strong pull-up/pull-down

resistance is approximately 33Ω, and the weak pull-up/pull-down resistance is approximately 4.7kΩ.

Because it is possible to switch the polarity and drive strength of

nTRST

and

nSRST

, target systems

with various different reset configurations are supported.

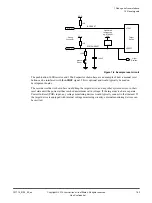

Example reset circuit

A typical reset circuit which would be present on the target board, is:

1 Debug and trace interface

1.3 Reset signals

101714_0100_02_en

Copyright © 2019 Arm Limited or its affiliates. All rights reserved.

1-19

Non-Confidential