1.9

Typical SWD circuit

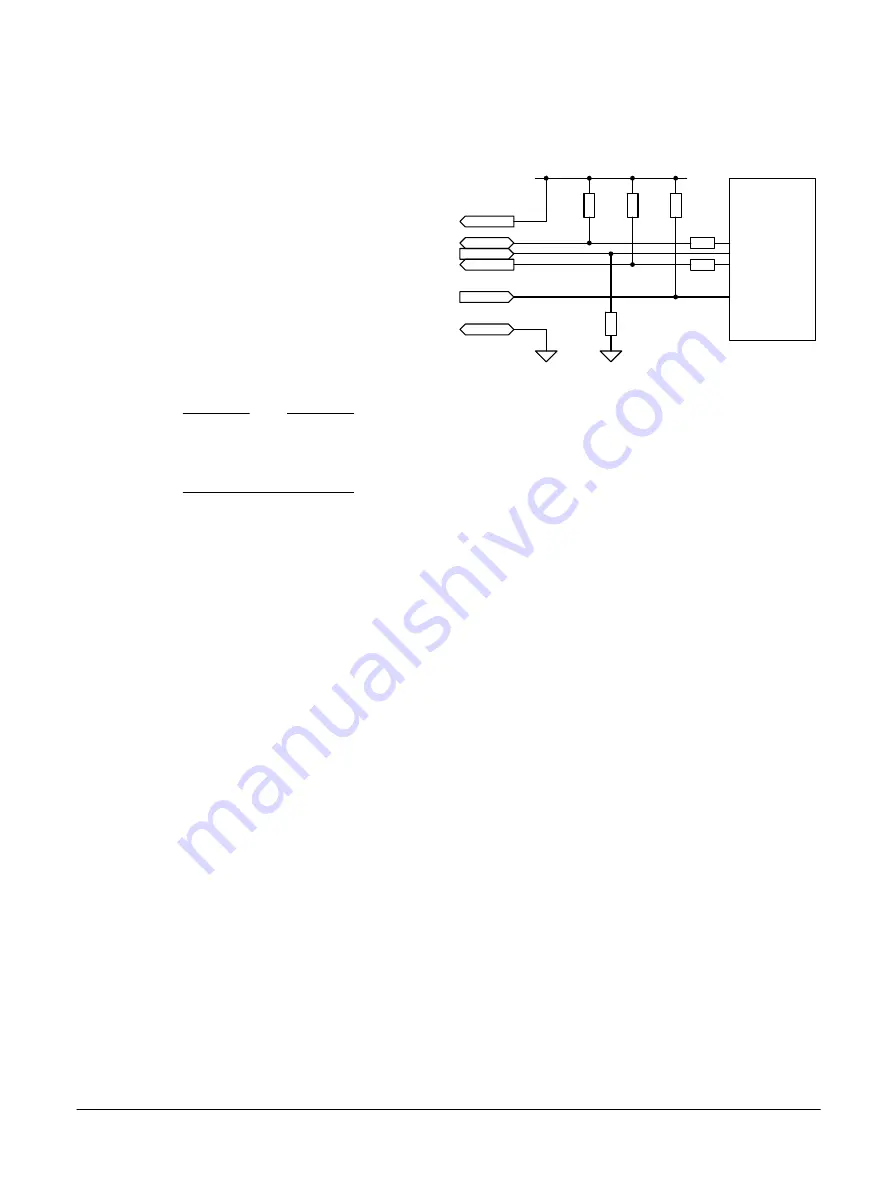

A typical SWD circuit:

10K

22R

Target

Device

VDD

Debug

Connector

VTREF

SWDIO

SWCLK

SWO

nSRST

GND

SWDIO

SWCLK

SWO

nRESET

10K

10K

22R

10K

Figure 1-17 Typical SWD circuit

Note

To improve signal integrity, it is good practice to provide an impedance-matching resistor on the

SWDIO

and

SWO

outputs of the processor. The value of these resistors, added to the impedance of the

driver, must be approximately equal to 50Ω.

1 Debug and trace interface

1.9 Typical SWD circuit

101714_0100_02_en

Copyright © 2019 Arm Limited or its affiliates. All rights reserved.

1-30

Non-Confidential