1.10

Typical JTAG circuit

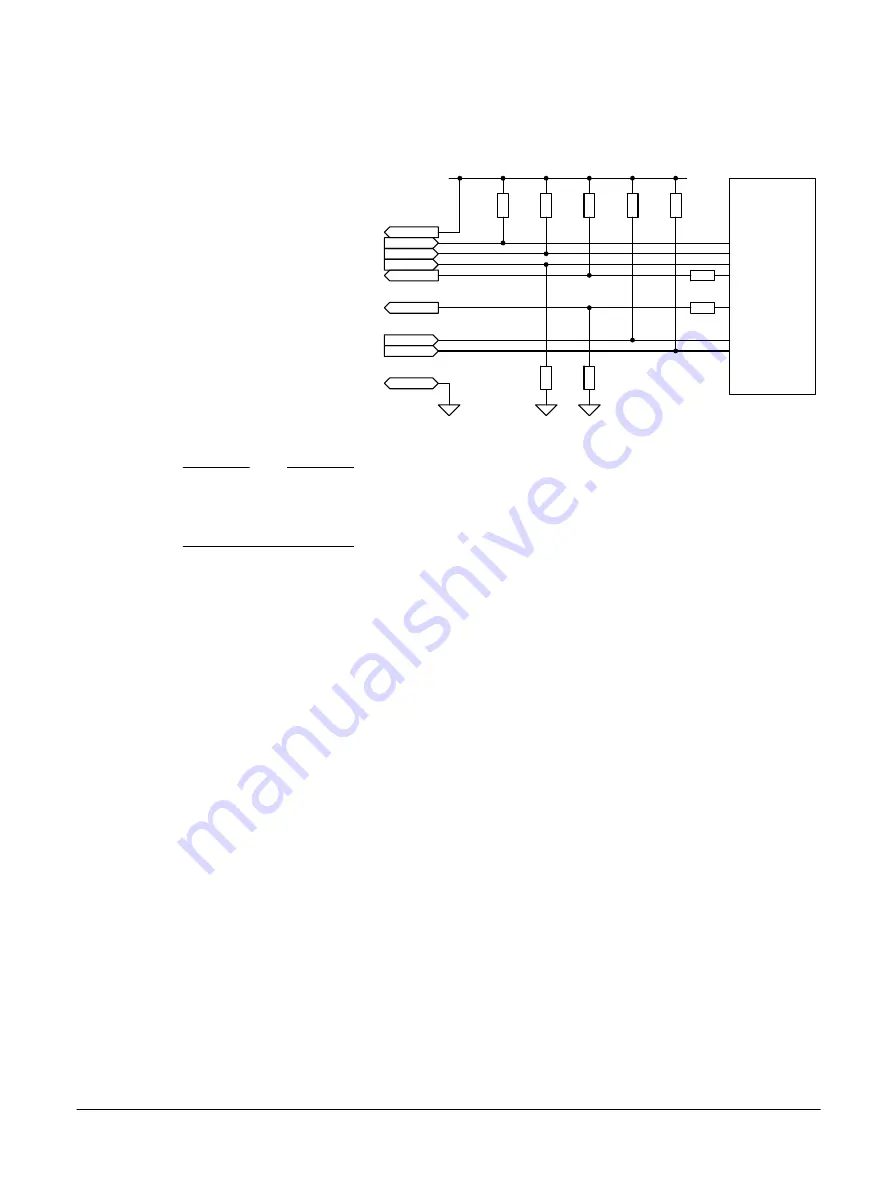

A typical JTAG circuit:

Target

Device

TDO

22R

RTCK

22R

VTREF

TDI

TMS

TCK

TDO

RTCK

nTRST

nSRST

GND

VDD

10K

10K

10K

10K

10K

TCK

TMS

TDI

nTRST

nRESET

10K

10K

Debug

Connector

Figure 1-18 Typical JTAG circuit

Note

To improve signal integrity, it is good practice to provide an impedance matching resistor on the

TDO

and

RTCK

outputs of the processor. The value of these resistors, added to the impedance of the driver,

must be approximately equal to 50Ω.

1 Debug and trace interface

1.10 Typical JTAG circuit

101714_0100_02_en

Copyright © 2019 Arm Limited or its affiliates. All rights reserved.

1-31

Non-Confidential