Functional Description

ARM DDI 0275D

Copyright © 2002, 2003 ARM Limited. All rights reserved.

2-17

2.10

Clocks, and resets

This section describes:

•

•

2.10.1

Clocks

The ETB11 has three clock domains:

•

TAP controller, clocked by

DBGTCK

•

memory-mapped peripheral, clocked by

HCLK

•

remainder of the system including ETB11 registers, clocked by

CLK

.

DBGTCK is synchronous to CLK when used with ETM11RV. Synchronization issues

can therefore be ignored and are not discussed further. See

on page 1-5 for details of other ETB products,

HCLK can be synchronous or asynchronous to CLK depending on your system design.

Synchronization logic is provided for asynchronous designs. Register read and write

accesses, and RAM read and write accesses, using the AHB interface are described in:

•

•

2.10.2

Resets

There are the following resets:

•

nRESET

resets all of the ETB11 registers in the

CLK

domain.

nRESET

must

be synchronized to

CLK

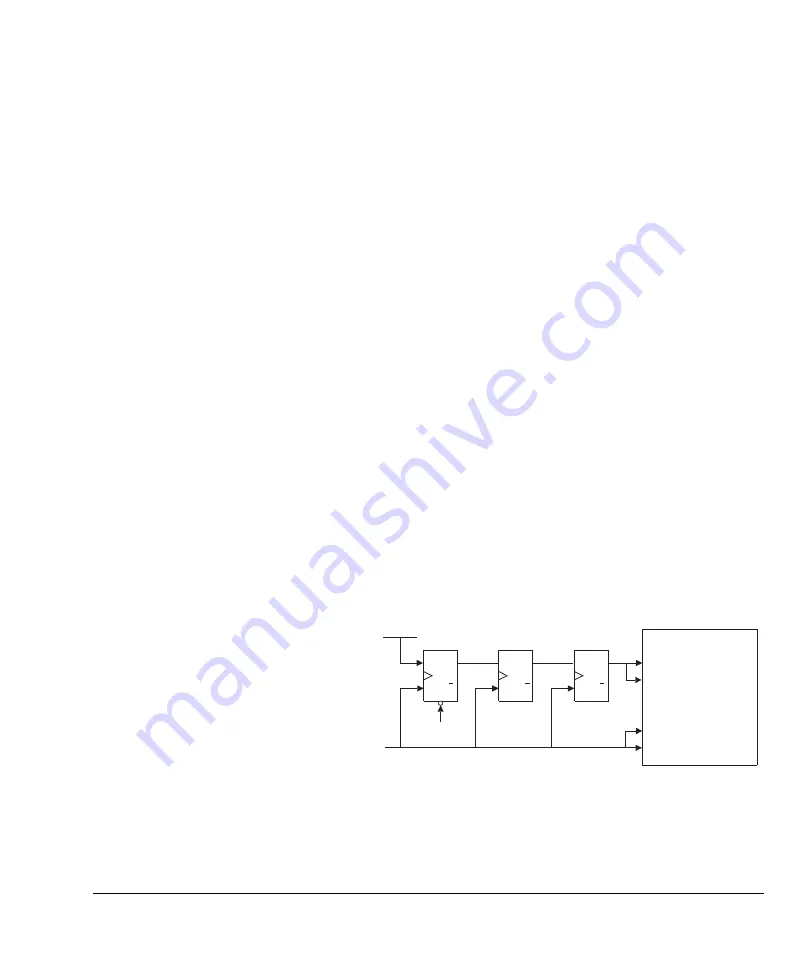

using the circuit shown in Figure 2-7.

Figure 2-7 Example synchronizer

•

nDBGTRST

is the TAP controller reset signal used to reset the ETB11 TAP

controller and other

DBGTCK

domain registers.

nDBGTRST

must be

synchronized to CLK using the circuit shown in Figure 2-7.

DBGnTRST

CLK

Q

Q

Q

Q

D

D

Q

Q

DBGTCK

CLK

nDBGTRST

nRESET

ETB11

+ve

Summary of Contents for ETB11

Page 6: ...List of Tables vi Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 8: ...List of Figures viii Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 46: ...Functional Description 2 26 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 70: ...Signal Descriptions A 6 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 78: ...Glossary Glossary 4 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...