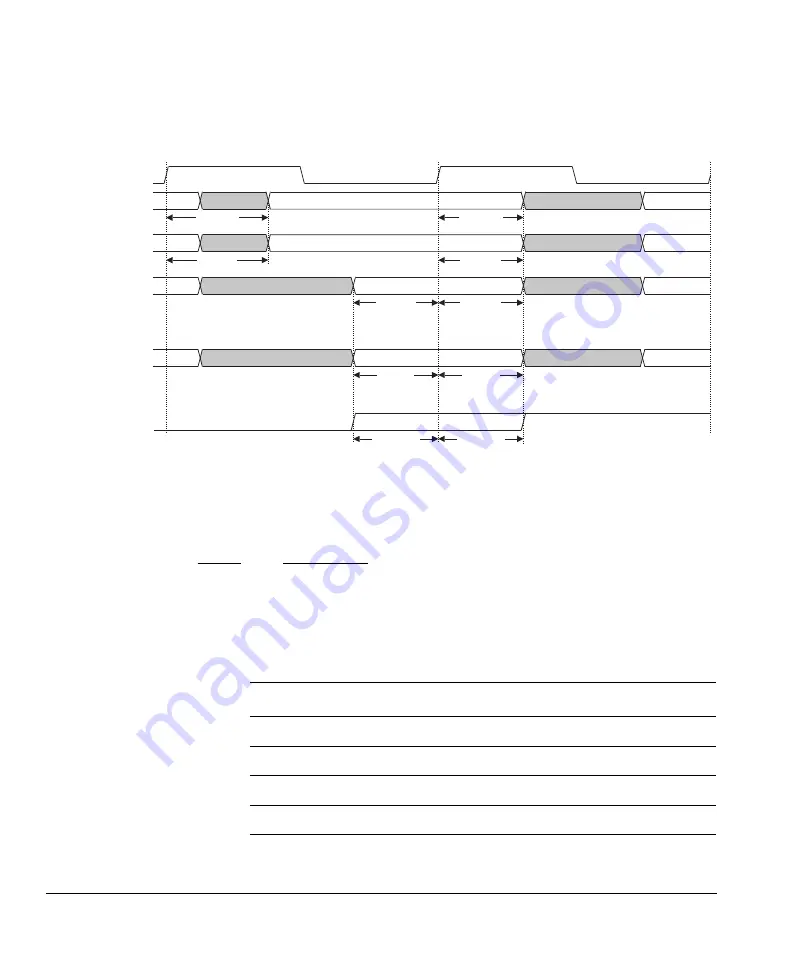

Timing Requirements

4-2

Copyright © 2002, 2003 ARM Limited. All rights reserved.

ARM DDI 0275D

4.1

AHB interface

The timings for the AHB interface signals are shown in Figure 4-1.

Figure 4-1 AHB interface signals

The timing requirements for the AHB interface are listed in Table 4-1. All figures are

expressed as percentages of the

HCLK

period at maximum operating frequency.

Note

A 0% figure in Table 4-1 indicates the hold time to clock edge plus the maximum clock

skew for internal clock buffering.

T

ihhresetn

T

ishresetn

T

ihhcon

T

ishcon

T

ihhdata

T

ishdata

T

ohhcon

T

ovhcon

T

ohhdata

T

ovhdata

HADDR,

HWDATA

HRDATAMEM

HCLK

HRESP,

HREADYMEM

HWRITE,

HTRANS,

HSIZE,

HREADY,

HSELREG,

HSELMEM

HRESETn

Table 4-1 AHB interface timing requirements

Parameter

Description

Max Min

T

ovhdata

Rising

HCLK

to

HRDATAMEM

valid

40%

-

T

ohhdata

HRDATAMEM

hold time from

HCLK

rising

-

>0%

T

ovhcon

Rising

HCLK

to AHB control outputs valid

40%

-

T

ohhcon

AHB control outputs hold time from

HCLK

rising

-

>0%

T

ishdata

AHB data inputs setup to rising

HCLK

-

30%

Summary of Contents for ETB11

Page 6: ...List of Tables vi Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 8: ...List of Figures viii Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 46: ...Functional Description 2 26 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 70: ...Signal Descriptions A 6 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...

Page 78: ...Glossary Glossary 4 Copyright 2002 2003 ARM Limited All rights reserved ARM DDI 0275D ...