Maps and Registers

ATCA-7360 Installation and Use (6806800J07S)

155

6.3.1

Register Decoding

The FPGA registers may be accessed from the host or the IPMC. For the host the LPC bus

interface is used. The IPMC uses an SPI interface.

0 or 1

Default value after PWR_GOOD is valid or after ICH_PLTRST

deassertion.

Undef. Undefined

value

<reset>: 0 or 1

Default value after deassertion of the reset signal <reset>.

Ext.

External Reset Source. Default depends on external logic level.

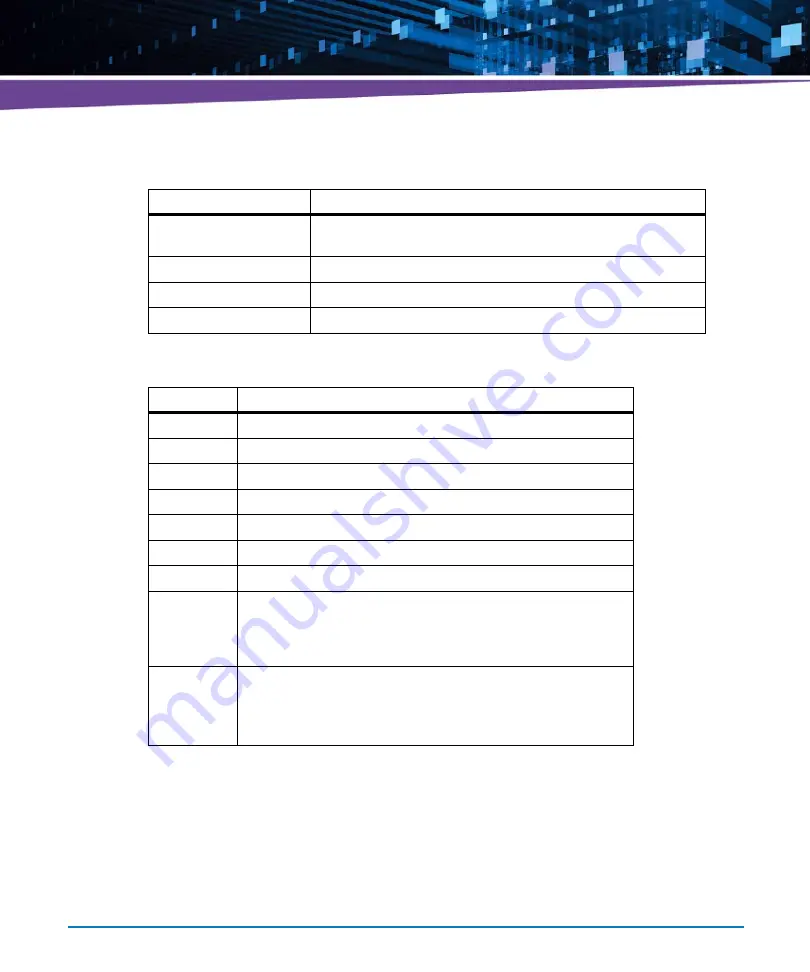

Table 6-5 Register Access Type

Access

Description

r Read

only

w Write

only

r/w

Read and write

w1c

Write-1-to-clear, ignore bit while reading

r/w1c

Read and write-1-to-clear, write 0 has no effect

r/w1s

Read and write-1-to-set, write 0 has no effect

r/w1t

Read and write-1-to-toggle, write 0 has no effect

LPC:

The prefix “LPC:” signals that the access is restricted to the LPC

interface.

E. g.: LPC: r/w means that the register bit is read/writable from the

LPC interface

IPMC:

The prefix “IPMC:” signals that the access is restricted to the IPMC

SPI interface.

For example, IPMC: r/w means that the register bit is read/writable

from IPMC SPI interface

Table 6-4 Register Default (continued)

Default

Description

Summary of Contents for ATCA-7360

Page 1: ...ATCA 7360 Installation and Use P N 6806800J07S May 2016...

Page 26: ...ATCA 7360 Installation and Use 6806800J07S About this Manual 26 About this Manual...

Page 36: ...ATCA 7360 Installation and Use 6806800J07S Sicherheitshinweise 36...

Page 43: ...Introduction ATCA 7360 Installation and Use 6806800J07S 43...

Page 44: ...Introduction ATCA 7360 Installation and Use 6806800J07S 44...

Page 66: ...Installation ATCA 7360 Installation and Use 6806800J07S 66...

Page 258: ...Supported IPMI Commands ATCA 7360 Installation and Use 6806800J07S 258...

Page 284: ...Replacing the Battery ATCA 7360 Installation and Use 6806800J07S 284...

Page 287: ......