Maps and Registers

ATCA-7360 Installation and Use (6806800J07S)

209

A write access to Telecom Timer MSB Register load the 16 bit Telecom timer with the write data

of the current access and the content of the Telecom Timer LSB Register.

6.4.23 Miscellaneous Status/Control Registers

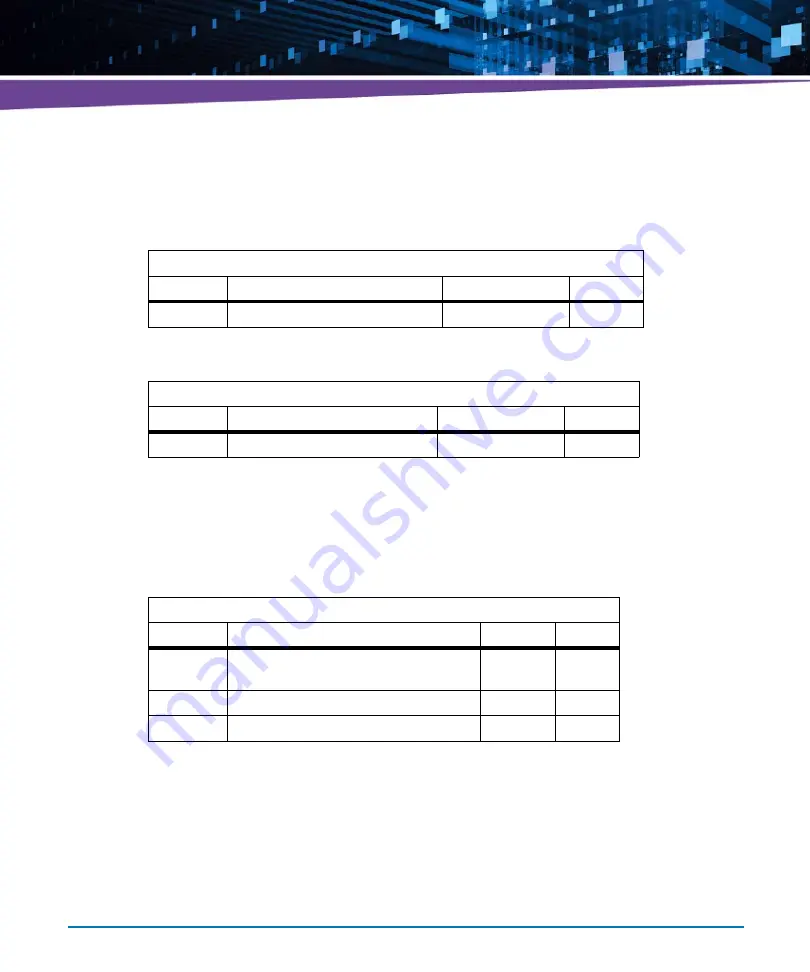

Table 6-81 Telecom Timer MSB Register

Address Offset: 0x65

Bit

Description

Default

Access

7:0

MSB of Telecom Timer start value

PWR_GOOD: 0

LPC: r/w

Table 6-82 Telecom Timer LSB Register

Address Offset: 0x64

Bit

Description

Default

Access

7:0

LSB of Telecom Timer start value

PWR_GOOD: 0

LPC: r/w

Table 6-83 CPLD Version and Spare Signal Status Register

Address Offset: 0x6F

Bit

Description

Default

Access

2:0

CPLD Version. The CPLD uses the signals

CPLD_SPARE[3:1]

Ext.

r

3

CPLD_SPARE[4]

Ext.

r

7:4

Reserved 0

r

Summary of Contents for ATCA-7360

Page 1: ...ATCA 7360 Installation and Use P N 6806800J07S May 2016...

Page 26: ...ATCA 7360 Installation and Use 6806800J07S About this Manual 26 About this Manual...

Page 36: ...ATCA 7360 Installation and Use 6806800J07S Sicherheitshinweise 36...

Page 43: ...Introduction ATCA 7360 Installation and Use 6806800J07S 43...

Page 44: ...Introduction ATCA 7360 Installation and Use 6806800J07S 44...

Page 66: ...Installation ATCA 7360 Installation and Use 6806800J07S 66...

Page 258: ...Supported IPMI Commands ATCA 7360 Installation and Use 6806800J07S 258...

Page 284: ...Replacing the Battery ATCA 7360 Installation and Use 6806800J07S 284...

Page 287: ......