500-003111-000

4-13

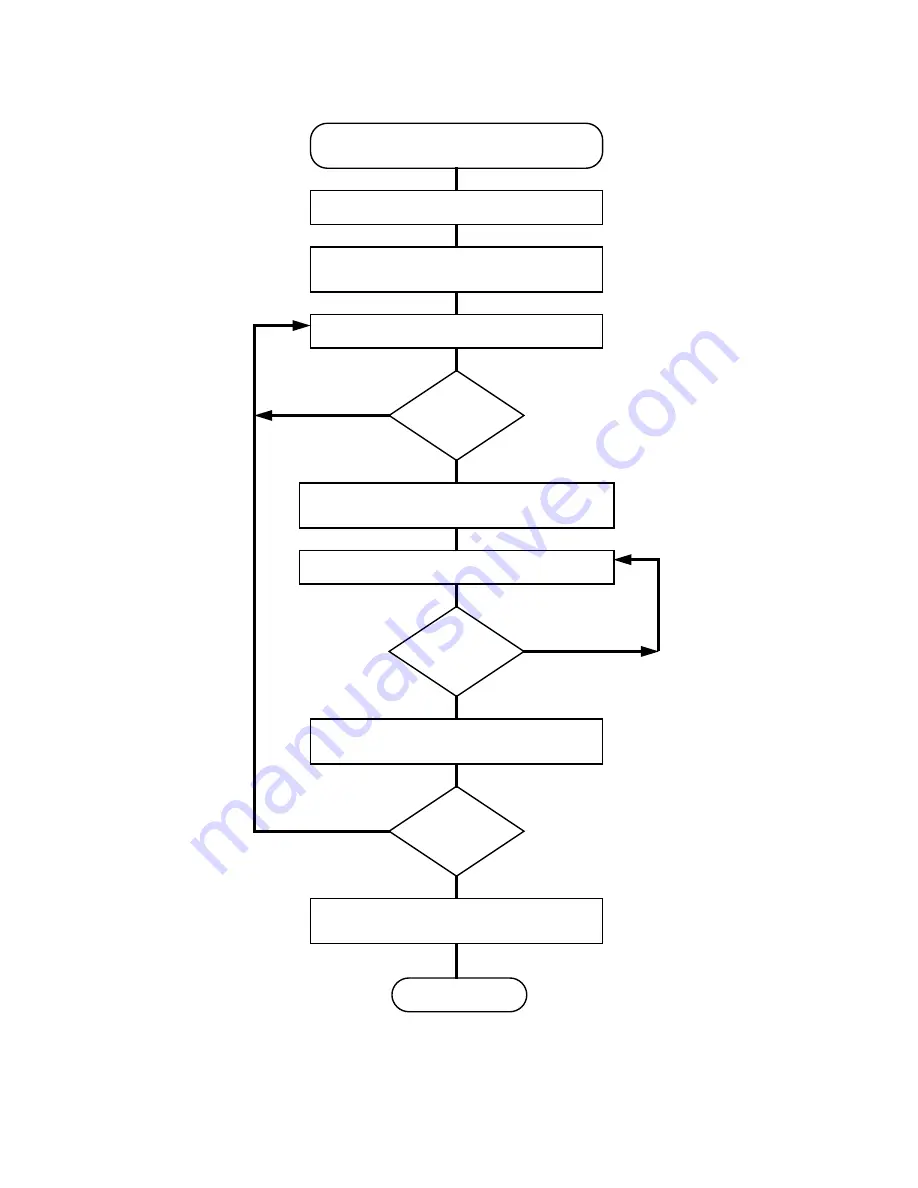

BEGIN SEQUENCE:

CONVERTER INTERLEAVED CONTROL

INITIALIZE TABLE POINTERS

SELECT FIRST INPUT CHANNEL; START

SETTLING AND CONVERSION SEQUENCES

READ STATUS REGISTER

SETTLING

BUSY?

START CONVERSION; WAIT FOR "CONV BUSY;"

SELECT NEXT CHANNEL; START SETTLING

READ STATUS REGISTER

DATA

READY?

READ DATA REGISTER;

STORE DATA IN MEMORY

LAST

CHANNEL

SELECTED?

END SEQUENCE

Figure 4.6.2-3. Program Flowchart - Pipelined ADC Control Sequence

YES

NO

YES

NO

NO

YES

M3111/F4.6.2-3

READ LAST CHANNEL

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com