60

3

VMIVME-3126A High Resolution, Isolated Analog-to-Digital Converter Board

Control and Status Register Bit Definitions (Continued)

Bit 13:

Open Sensor -

This bit enables the Open Sensor detection on the

inputs when set to a logical one (1). The default condition is a

logic zero (0). The range for the channel must be less than or

equal to ±1 V (0 to 1 V) for open sensor detect to work properly.

Refer to Table 3-15 below for the code to enter for these ranges.

This bit is reset automatically by the DSP after the open-sensor

detection has completed. Status of whether or not the sensor was

open is reported in the PFS register.

Bit 12 and Bits 07 through 03:

Reserved -

Set these bits to a logical zero (0).

Bits 11 through 08:

Range Bits [3...0] -

This field determines the input range for the

channel. The range code is used by the DSP to determine the

channel gain. Table 3-15 below shows the range code and

associated input voltage range.

Bits 02 through 00:

FC [2...0] -

This field is the channel’s -3 dB cutoff frequency as

shown in Table 3-16 on page 61 below. The default setting is 111.

NOTE:

1

Denotes default setting for a normal voltage board.

2

Denotes default setting for a

low level voltage board.

3

Only available with the low level voltage option.

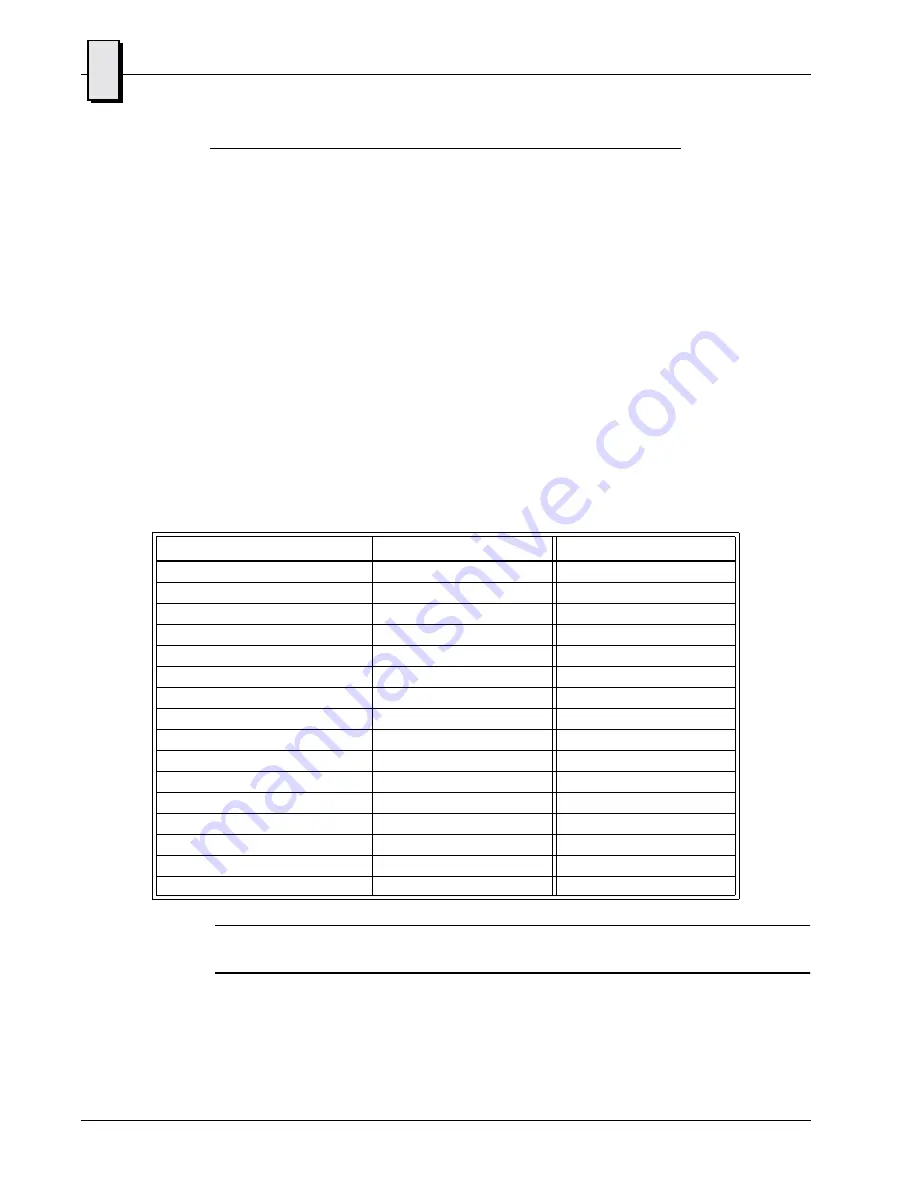

Table 3-15 Input Range Control

Range Code (HEX)

Input Range

Notes

0

0-10 V

1

0-5 V

2

0-1 V

3

0-500 mV

4

0-100 mV

5

0-50 mV

6

0-20 mV

3

7

Reserved

8

±

10 V

1

9

±

5 V

A

±

1 V

2

B

±

500 mV

C

±

100 mV

D

±

50 mV

E

±

20 mV

3

F

±

5 mV

3

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com