Summary of Contents for AAEON BOXER-6642-CML

Page 1: ...Last Updated April 7 2021 BOXER 6642 CML Fanless Embedded Box PC User s Manual 1st Ed ...

Page 15: ...Fanless Embedded Box PC BOXER 6642 CML Chapter 1 Chapter 1 Product Specifications ...

Page 18: ...Fanless Embedded Box PC BOXER 6642 CML Chapter 2 Chapter 2 Hardware Information ...

Page 19: ...Chapter 2 Hardware Information 5 Fanless Embedded Box PC BOXER 6642 CML 2 1 Dimensions System ...

Page 20: ...Chapter 2 Hardware Information 6 Fanless Embedded Box PC BOXER 6642 CML Board Dimensions ...

Page 49: ...Fanless Embedded Box PC BOXER 6642 CML Chapter 3 Chapter 3 AMI BIOS Setup ...

Page 52: ...Chapter 3 AMI BIOS Setup 38 Fanless Embedded Box PC BOXER 6642 CML 3 3 Setup Submenu Main ...

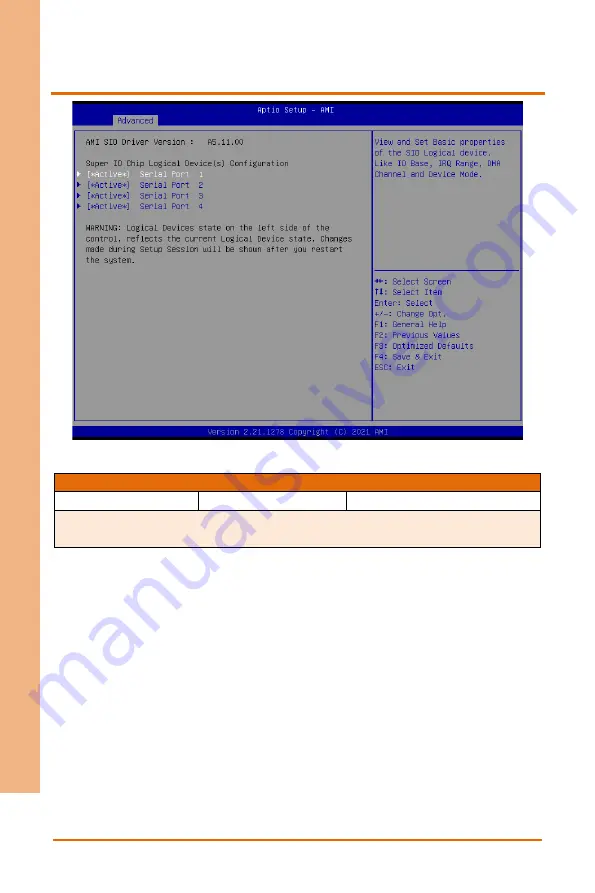

Page 53: ...Chapter 3 AMI BIOS Setup 39 Fanless Embedded Box PC BOXER 6642 CML 3 4 Setup Submenu Advanced ...

Page 64: ...Chapter 3 AMI BIOS Setup 50 Fanless Embedded Box PC BOXER 6642 CML 3 4 7 Hardware Monitor ...

Page 72: ...Chapter 3 AMI BIOS Setup 58 Fanless Embedded Box PC BOXER 6642 CML 3 5 Setup Submenu Chipset ...

Page 83: ...Fanless Embedded Box PC BOXER 6642 CML Chapter 4 Chapter 4 Drivers Installation ...

Page 86: ...Fanless Embedded Box PC BOXER 6642 CML Appendix A Appendix A Watchdog Timer Programming ...

Page 92: ...Fanless Embedded Box PC BOXER 6642 CML Appendix B Appendix B I O Information ...

Page 93: ...Appendix B I O Information 79 Fanless Embedded Box PC BOXER 6642 CML B 1 I O Address Map ...

Page 94: ...Appendix B I O Information 80 Fanless Embedded Box PC BOXER 6642 CML ...

Page 95: ...Appendix B I O Information 81 Fanless Embedded Box PC BOXER 6642 CML B 2 IRQ Mapping Chart ...

Page 96: ...Appendix B I O Information 82 Fanless Embedded Box PC BOXER 6642 CML B 3 Memory Address Map ...

Page 97: ...Appendix B I O Information 83 Fanless Embedded Box PC BOXER 6642 CML ...

Page 98: ...Fanless Embedded Box PC BOXER 6642 CML Appendix C Appendix C Digital I O Ports ...

Page 102: ...Appendix C Digital I O Information 88 Fanless Embedded Box PC BOXER 6642 CML ...

Page 109: ...Fanless Embedded Box PC BOXER 6642 CML Appendix D Appendix D Glue Removal Procedure ...