Armadillo-9

hardware manual ver.1.02

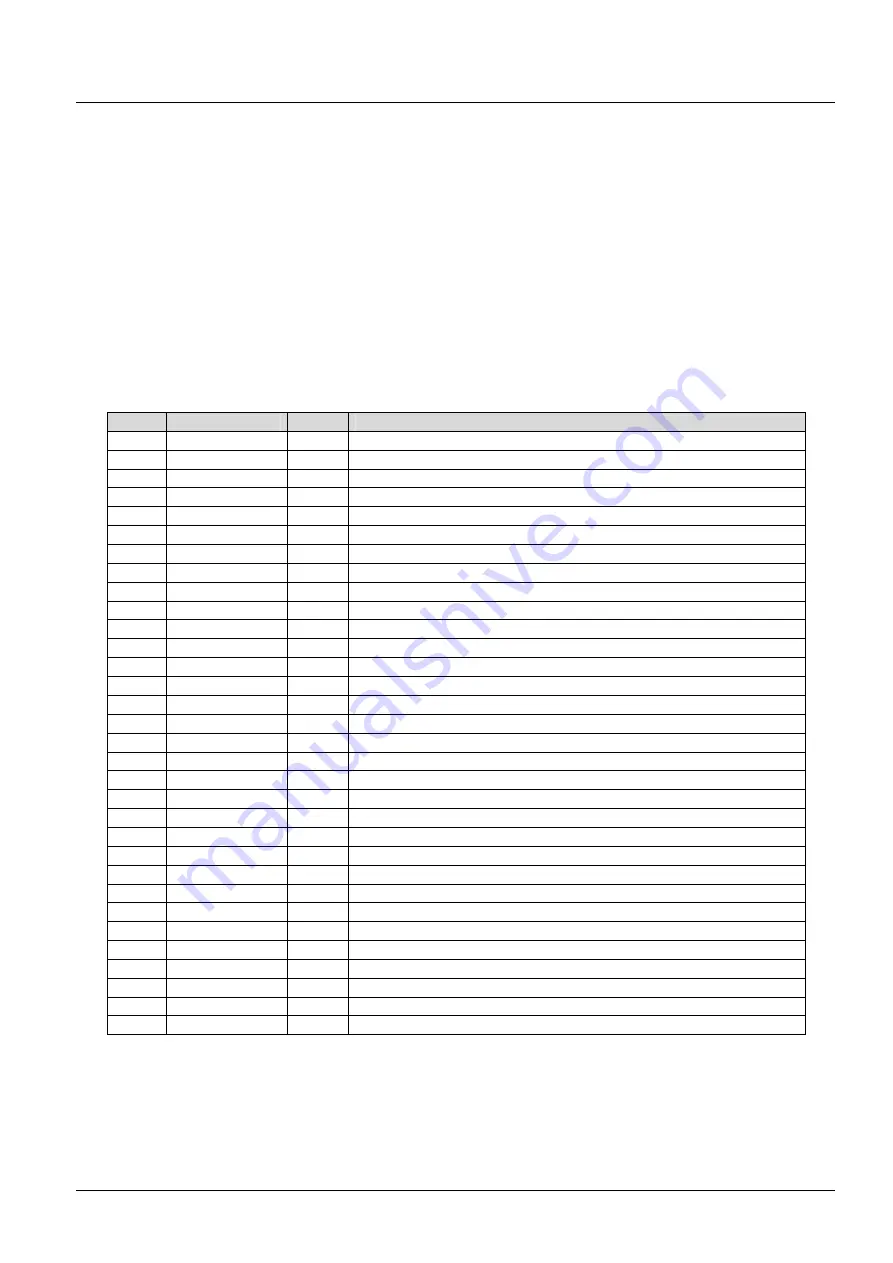

5.16. J1, J2 (PC/104-Compliant Extension Bus)

J1 and J2 are extension buses with PC/104-compliant bus arrays. They have a 64kB I/O area and a

16MB memory area. However, since the ARM architecture does not have an I/O area (I/O access only) as

x86 CPUs do, the I/O area is placed in the standard memory space.

The extension buses are a subset of the PC/104 standard. Main differences with the standard PC/104

bus are as follows:

Non-support of dynamic bus sizing

Non-support of DMA (DREQ / DACK)

Non-support of external master

Fixed bus access cycle

Table 5-17 J1 Signal Assignment (1)

No.

Signal Name

I/O

Function

A1 IOCHCHK*

(I) Non-support

A2

D7

I/O

Data bus (bit7)

A3

D6

I/O

Data bus (bit6)

A4

D5

I/O

Data bus (bit5)

A5

D4

I/O

Data bus (bit4)

A6

D3

I/O

Data bus (bit3)

A7

D2

I/O

Data bus (bit2)

A8

D1

I/O

Data bus (bit1)

A9

D0

I/O

Data bus (bit0)

A10

IOCHRDY*

I

Extension of access cycle to match a low speed device

A11

AEN

O

Release of bus (GND)

A12 A19

O Address

bus

(bit19)

A13 A18

O Address

bus

(bit18)

A14 A17

O Address

bus

(bit17)

A15 A16

O Address

bus

(bit16)

A16 A15

O Address

bus

(bit15)

A17 A14

O Address

bus

(bit14)

A18 A13

O Address

bus

(bit13)

A19 A12

O Address

bus

(bit12)

A20 A11

O Address

bus

(bit11)

A21 A10

O Address

bus

(bit10)

A22 A9

O Address

bus

(bit9)

A23 A8

O Address

bus

(bit8)

A24 A7

O Address

bus

(bit7)

A25 A6

O Address

bus

(bit6)

A26 A5

O Address

bus

(bit5)

A27 A4

O Address

bus

(bit4)

A28 A3

O Address

bus

(bit3)

A29 A2

O Address

bus

(bit2)

A30 A1

O Address

bus

(bit1)

A31 A0

O Address

bus

(bit0)

A32

GND

Power Power supply (GND)

17