How to Calculate the Capacitor of the Reset

Input of a C51 Microcontroller

This application note explains how the reset of the 80C51 microcontroller works when

the RST pin is a pure input pin and when the RST input is bi-directional. It gives rules

to determine the extra components required to operate the reset function properly.

The reset process can be active on low or high level depending on the product. In this

application note only the high level case is discussed.

Introduction

The reset is used to start-up or to restart the 80C51 microcontroller activities. It forces

the 80C51 in a known state by reinitializing all the internal registers needed to properly

start the program execution. The reset must be kept active until all three of the follow-

ing conditions are respected:

•

The power supply must be in the specified range.

•

The oscillator must reach a minimum oscillation level to ensure a good noise to

signal ratio and a correct internal duty cycle generation.

•

The reset pulse width duration must be at least two machine cycles.

If one of the conditions is not respected the microcontroller will not startup properly.

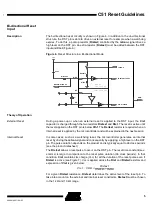

Theory of Reset Operation

To ensure a good startup, the reset pulse width has to be wide enough to cover the

period of time where the electrical conditions are not met. Two parameters should be

considered for a proper reset sequence to determine the reset pulse width (see

Figure 1):

•

t

osc

: time needed by the oscillator to reach the Vih1 or Vil1 level.

•

t

vddrise

: rise time of the power-supply taken between 10 to 90% of V

DD

.

When these two parameter conditions are met, the reset has to be maintained at least

two machine cycles in order to synchronize the internal activity of the core. In normal

mode, a machine cycle is 12-clock periods and in X2 mode is 6-clock periods.

Rev. 4284A–8051–09/03

80C51

Microcontrollers

Application Note