6

C51 Reset Guidelines

4284A–8051–09/03

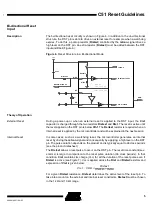

Figure 7. Reset Circuitry When an Internal Reset is Applied

Without Rrstext no external reset signal will be generated.

Use Excel File to

Determine Crst

To determine Crst, the reset pulse width needs to be calculated using the following

equation:

treset = t

vddrise

+ t

osc

•

t

vddrise

(typically 1 ms to 100 ms), is the rise time of the V

DD

(10% and 90% of the

V

DD

). It depends on the power supply and the decoupling capacitors used.

•

t

osc

(typically 1 ms to 50 ms), time taken by the oscillator at startup. It depends on

the crystal characteristics and the capacitors connected to the crystal.

Because the power supply has a finite transition time (several hundreds of microsec-

onds to several milliseconds), Crst is not so easy to compute by hand. Excel tool is

used to calculate Crst versus t

vddrise

and t

osc

parameters. A spreadsheet can be down-

loaded from the Atmel Web site to compute Crst.

Four parameters have to be entered and Crst is directly computed by the spreadsheet

while 1k

Ω

is chosen for Rrst. Here is how to do it:

•

V

DD

, the power supply voltage, is entered in the cell F3

•

t

vddrise

, the rise time of the power-supply, is entered in the cell F4

•

t

osc

, the oscillator startup time, is entered in cell F8

•

Rrstmin, the minimum pull-down resistor, is entered in the cell F13

After these steps, the cell E31 has to be clicked to compute the Crst and the minimum

reset pulse width.

0

VDD

0

Rrstwt

Rrst

Rrstext

Crst

Internal reset

V

DD

Vrst

Vih1