256

4317I–AVR–01/08

AT90PWM2/3/2B/3B

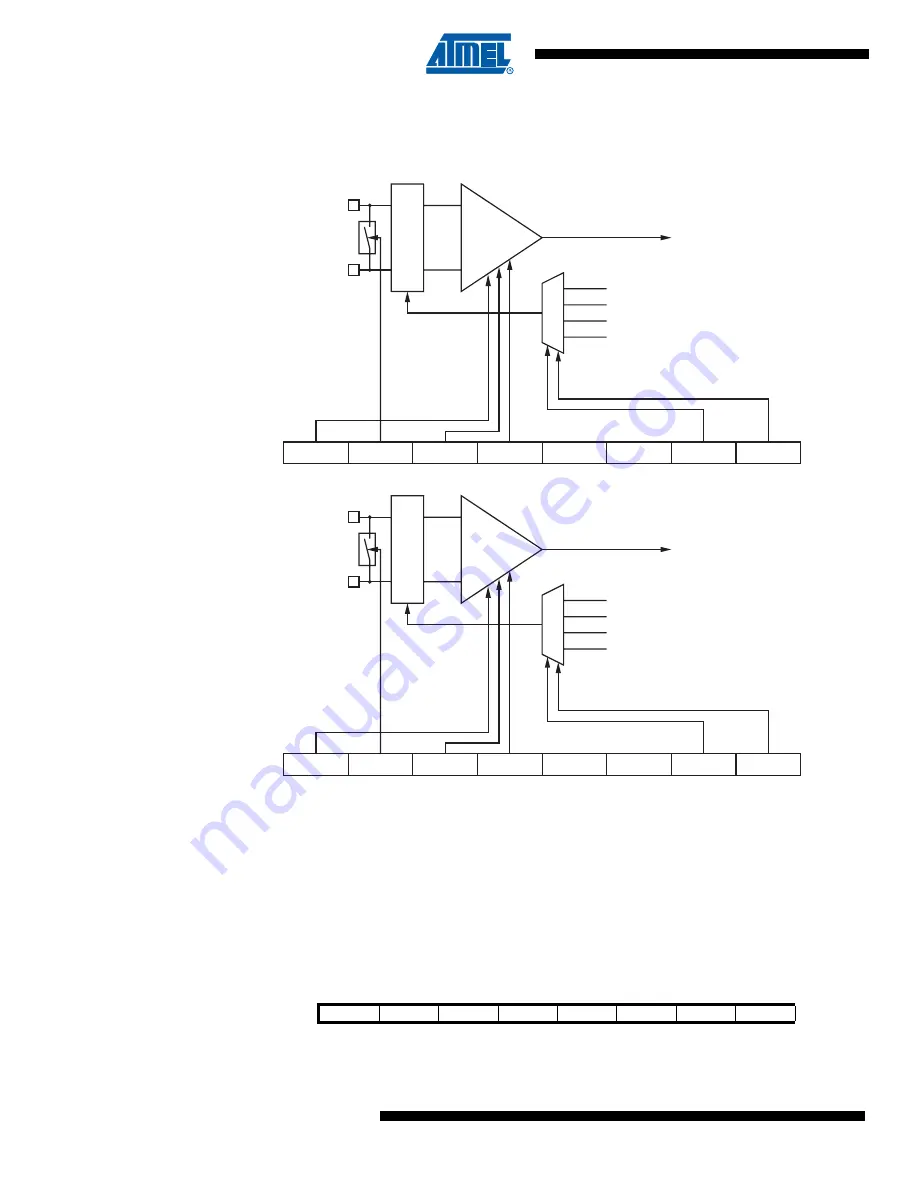

The block diagram of the two amplifiers is shown on

Figure 21-18. Amplifiers block diagram

21.10 Amplifier Control Registers

The configuration of the amplifiers are controlled via two dedicated registers AMP0CSR and

AMP1CSR. Then the start of conversion is done via the ADC control and status registers.

The conversion result is stored on ADCH and ADCL register which contain respectively the most

significant bits and the less significant bits.

21.10.1

Amplifier 0 Control and Status register – AMP0CSR

AMP0TS1AMP0TS0

AMP0EN AMP0IS AMP0G1 AMP0G0

AMP0CSR

+

-

SAMPLING

AMP0+

AMP0-

Toward ADC MUX

(AMP0)

Sampling

Clock

ADCK/8

01

10

01

00

ASY0

ASY1

ASY2

-

-

AMP1TS1AMP1TS0

AMP1EN AMP1IS AMP1G1 AMP1G0

AMP1CSR

+

-

SAMPLING

AMP1+

AMP1-

Toward ADC MU

(AMP1)

Sampling

Clock

ADCK/8

01

10

01

00

ASY0

ASY1

ASY2

-

-

Bit

7

6

5

4

3

2

1

0

AMP0EN

AMP0IS

AMP0G1

AMP0G0

-

-

AMP0TS1

AMP0TS0

AMP0CSR

Read/Write

R/W

R/W

R/W

R/W

-

-

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0