228

4317I–AVR–01/08

AT90PWM2/3/2B/3B

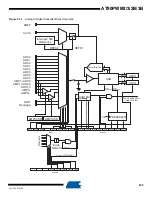

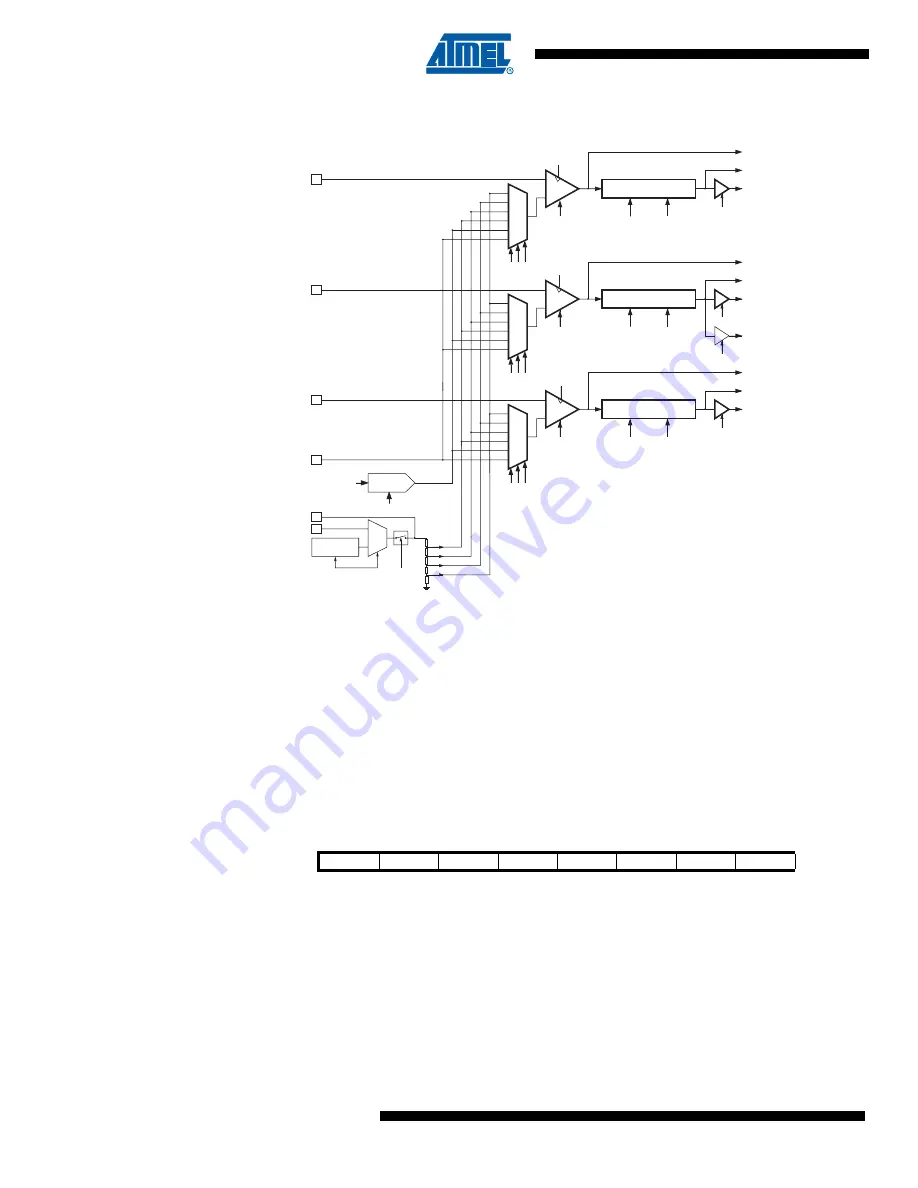

Figure 20-1. Analog Comparator Block Diagram

Notes:

1. ADC multiplexer output: see

2. Refer to

and for Analog Comparator pin placement.

3. The voltage on Vref is defined in

26 “ADC Voltage Reference Selection” on page 247

20.2

Analog Comparator Register Description

Each analog comparator has its own control register.

A dedicated register has been designed to consign the outputs and the flags of the 3 analog

comparators.

20.2.1

Analog Comparator 0 Control Register – AC0CON

• Bit 7– AC0EN: Analog Comparator 0 Enable Bit

Set this bit to enable the analog comparator 0.

Clear this bit to disable the analog comparator 0.

• Bit 6– AC0IE: Analog Comparator 0 Interrupt Enable bit

Set this bit to enable the analog comparator 0 interrupt.

Clear this bit to disable the analog comparator 0 interrupt.

• Bit 5, 4– AC0IS1, AC0IS0: Analog Comparator 0 Interrupt Select bit

+

-

Interrupt Sensitivity Control

Analog Comparator 0 Interrupt

AC0IE

AC0IF

AC0O

AC0IS1

AC0IS0

+

-

Interrupt Sensitivity Control

Analog Comparator 1 Interrupt

AC1IE

T1 Capture Trigger

AC1ICE

AC1IF

AC1O

AC1IS1

AC1IS0

+

-

Interrupt Sensitivity Control

Analog Comparator 2 Interrupt

AC0IE

AC2IF

AC2O

AC2IS1

AC2IS0

ACMP0

ACMP1

ACMP2

AC2EN

/3.20

/2.13

/1.60

/6.40

ACMPM

Vref

DAC

AC0M

2 1 0

DAC

Result

AC1EN

AC0EN

AC1M

2 1 0

AC2M

2 1 0

Internal 2.56V

Reference

REFS0

REFS1

Aref

AVcc

DACEN

CLK

I/O

CLK

I/O

CLK

I/O

(/2)

(/2)

(/2)

Bit

7

6

5

4

3

2

1

0

AC0EN

AC0IE

AC0IS1

AC0IS0

-

AC0M2

AC0M1

AC0M0

AC0CON

Read/Write

R/W

R/W

R/W

R/W

-

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0