7

6415B–ATARM–03-Oct-08

Application Note

5.4

PLLB

5.5

Processor/Master Clock

A new field (PDIV) has been added to program the processor speed.

5.6

SDRAM Clock

The rising and falling times of the EBI signals can be adapted using the “selectable drive func-

tion” located in the EBI_CSA register.

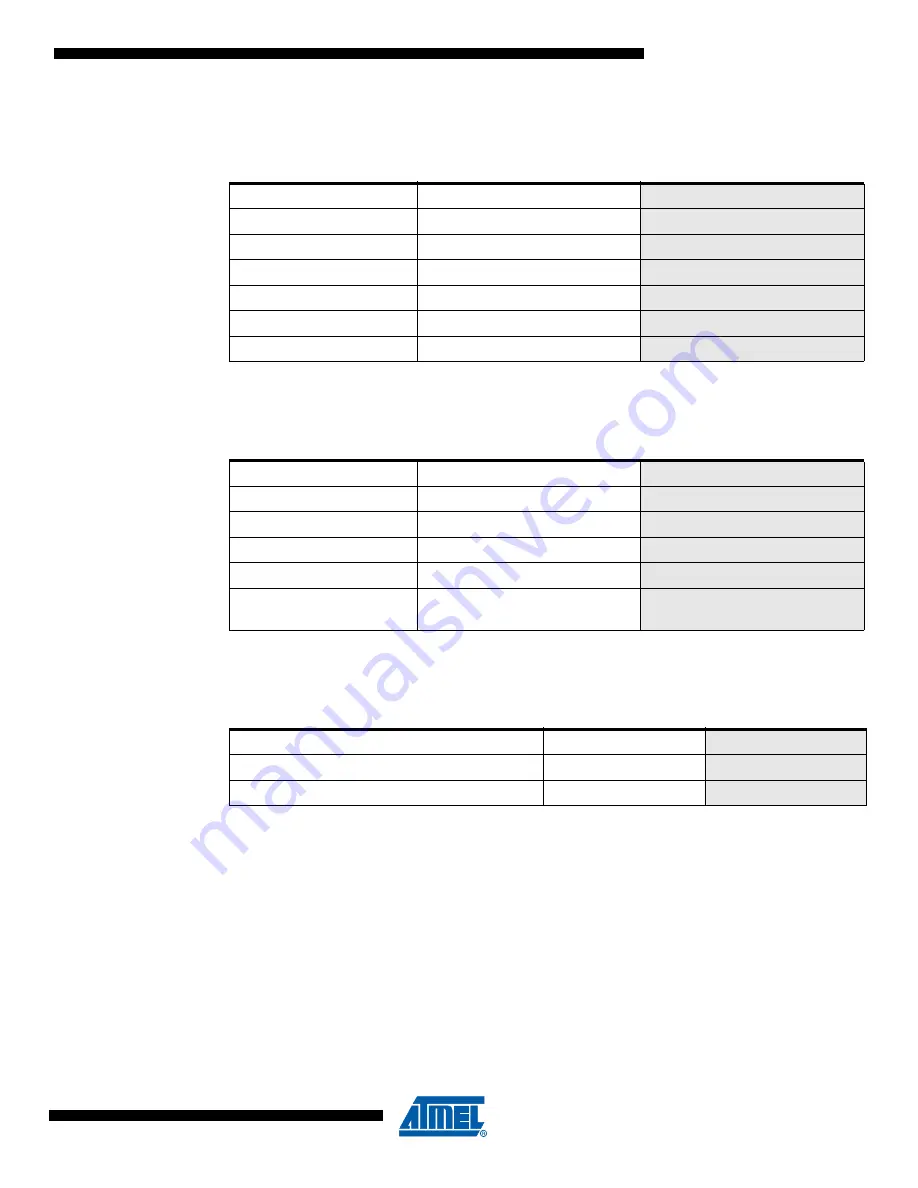

Table 5-9.

PLLB Characteristics

PLLB Characteristics

AT91SAM9260

AT91SAM9G20

Range

70 - 130 MHz

30 - 100 MHz

MULB

1 - 1047

1 - 62

DIVB

1 - 255

1 - 255

OUTB

01

00

Entry frequency

1 - 5 MHz

2 - 32 MHz

Embedded PLL Filter

Yes

Yes

Table 5-10.

Processor/Master Clock

Characteristics

AT91SAM9260

AT91SAM9G20

Processor Max frequency

180 MHz

400 MHz

Bus Max frequency

90 MHz

133 MHz

Master clock divider MDIV

1, 2, 4

1, 2, 4, 6

Processor clock div. PDIV

N/A

1, 2

Current consumption on

VDDCORE in Active Mode

130 mA @ 180 / 90 MHz

50 mA @ 400 / 133 MHz

Table 5-11.

SDRAM clocks

Characteristics

AT91SAM9260

AT91SAM9G20

SDCK Max frequency @ 1.8V (load = 30pF)

100 MHz

133 MHz

SDCK Max frequency @ 3.3V (load = 50pF)

100 MHz

133 MHz