12

2467S–AVR–07/09

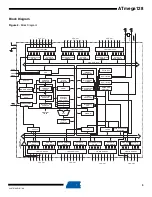

ATmega128

• Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual inter-

rupt enable control is then performed in separate control registers. If the Global Interrupt Enable

Register is cleared, none of the interrupts are enabled independent of the individual interrupt

enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by

the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared in

software with the SEI and CLI instructions, as described in the instruction set reference.

• Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or desti-

nation for the operated bit. A bit from a register in the Register file can be copied into T by the

BST instruction, and a bit in T can be copied into a bit in a register in the Register file by the BLD

instruction.

• Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a half carry in some arithmetic operations. Half carry is useful in

BCD arithmetic. See the “Instruction Set Description” for detailed information.

• Bit 4 – S: Sign Bit, S = N

⊕

V

The S-bit is always an exclusive or between the negative flag N and the two’s complement over-

flow flag V. See the “Instruction Set Description” for detailed information.

• Bit 3 – V: Two’s Complement Overflow Flag

The Two’s Complement Overflow Flag V supports two’s complement arithmetics. See the

“Instruction Set Description” for detailed information.

• Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the

“Instruction Set Description” for detailed information.

• Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the “Instruction

Set Description” for detailed information.

• Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set

Description” for detailed information.

General Purpose

Register File

The Register file is optimized for the AVR Enhanced RISC instruction set. In order to achieve the

required performance and flexibility, the following input/output schemes are supported by the

Register file:

•

One 8-bit output operand and one 8-bit result input

•

Two 8-bit output operands and one 8-bit result input

•

Two 8-bit output operands and one 16-bit result input

•

One 16-bit output operand and one 16-bit result input

shows the structure of the 32 general purpose working registers in the

CPU.