150

2467S–AVR–07/09

ATmega128

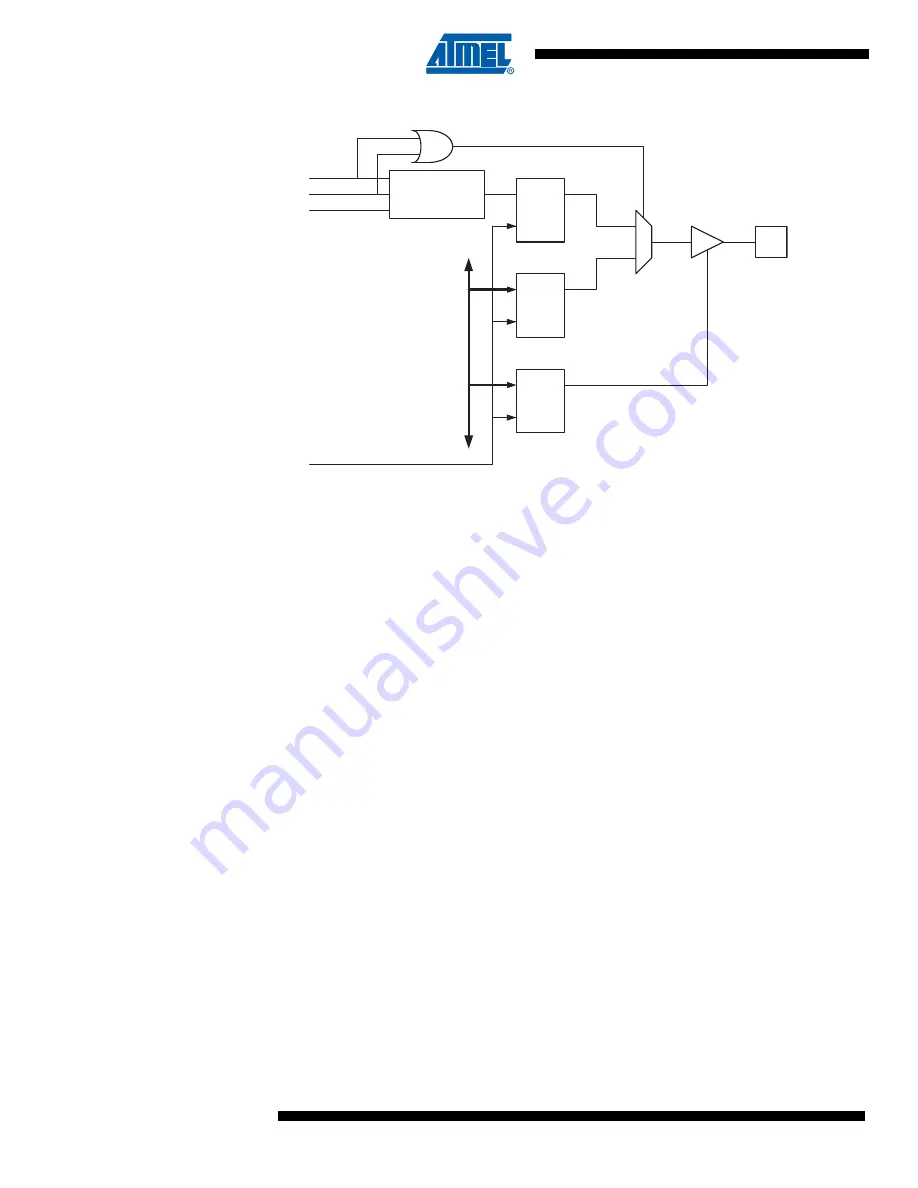

Figure 64.

Compare Match Output Unit, Schematic

The general I/O port function is overridden by the output compare (OC2) from the waveform

generator if either of the COM21:0 bits are set. However, the OC2 pin direction (input or output)

is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Regis-

ter bit for the OC2 pin (DDR_OC2) must be set as output before the OC2 value is visible on the

pin. The port override function is independent of the Waveform Generation mode.

The design of the output compare pin logic allows initialization of the OC2 state before the out-

put is enabled. Note that some COM21:0 bit settings are reserved for certain modes of

operation.

See “8-bit Timer/Counter Register Description” on page 157.

Compare Output Mode

and Waveform

Generation

The waveform generator uses the COM21:0 bits differently in normal, CTC, and PWM modes.

For all modes, setting the COM21:0 = 0 tells the waveform generator that no action on the OC2

Register is to be performed on the next compare match. For compare output actions in the non-

PWM modes refer to

and for phase correct PWM refer to

A change of the COM21:0 bits state will have effect at the first compare match after the bits are

written. For non-PWM modes, the action can be forced to have immediate effect by using the

FOC2 strobe bits.

Modes of

Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is

defined by the combination of the Waveform Generation mode (WGM21:0) and Compare Output

mode (COM21:0) bits. The Compare Output mode bits do not affect the counting sequence,

while the Waveform Generation mode bits do. The COM21:0 bits control whether the PWM out-

put generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes

the COM21:0 bits control whether the output should be set, cleared, or toggled at a compare

match (see “Compare Match Output Unit” on page 149).

For detailed timing information refer to

, and

“Timer/Counter Timing Diagrams” on page 155

.

Normal Mode

The simplest mode of operation is the normal mode (WGM21:0 = 0). In this mode the counting

direction is always up (incrementing), and no counter clear is performed. The counter simply

PORT

DDR

D

Q

D

Q

OCn

Pin

OCn

D

Q

Waveform

Generator

COMn1

COMn0

0

1

D

ATA

B

U

S

FOCn

clk

I/O