13

2467S–AVR–07/09

ATmega128

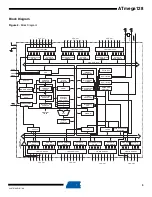

Figure 4.

AVR CPU General Purpose Working Registers

Most of the instructions operating on the Register file have direct access to all registers, and

most of them are single cycle instructions.

As shown in

, each register is also assigned a data memory address, mapping them

directly into the first 32 locations of the user Data Space. Although not being physically imple-

mented as SRAM locations, this memory organization provides great flexibility in access of the

registers, as the X-, Y-, and Z-pointer Registers can be set to index any register in the file.

X-register, Y-register,

and Z-register

The registers R26..R31 have some added functions to their general purpose usage. These reg-

isters are 16-bit address pointers for indirect addressing of the Data Space. The three indirect

address registers X, Y, and Z are described in

Figure 5.

The X-, Y-, and Z-registers

In the different addressing modes these address registers have functions as fixed displacement,

automatic increment, and automatic decrement (see the Instruction Set Reference for details).

7

0

Addr.

R0 $00

R1

$01

R2

$02

…

R13

$0D

General

R14

$0E

Purpose

R15

$0F

Working

R16

$10

Registers

R17

$11

…

R26

$1A

X-register Low Byte

R27

$1B

X-register High Byte

R28

$1C

Y-register Low Byte

R29

$1D

Y-register High Byte

R30

$1E

Z-register Low Byte

R31

$1F

Z-register High Byte

15

XH

XL

0

X - register

7

0

7

0

R27 ($1B)

R26 ($1A)

15

YH

YL

0

Y - register

7

0

7

0

R29 ($1D)

R28 ($1C)

15

ZH

ZL

0

Z - register

7

0

7

0

R31 ($1F)

R30 ($1E)