156

2467S–AVR–07/09

ATmega128

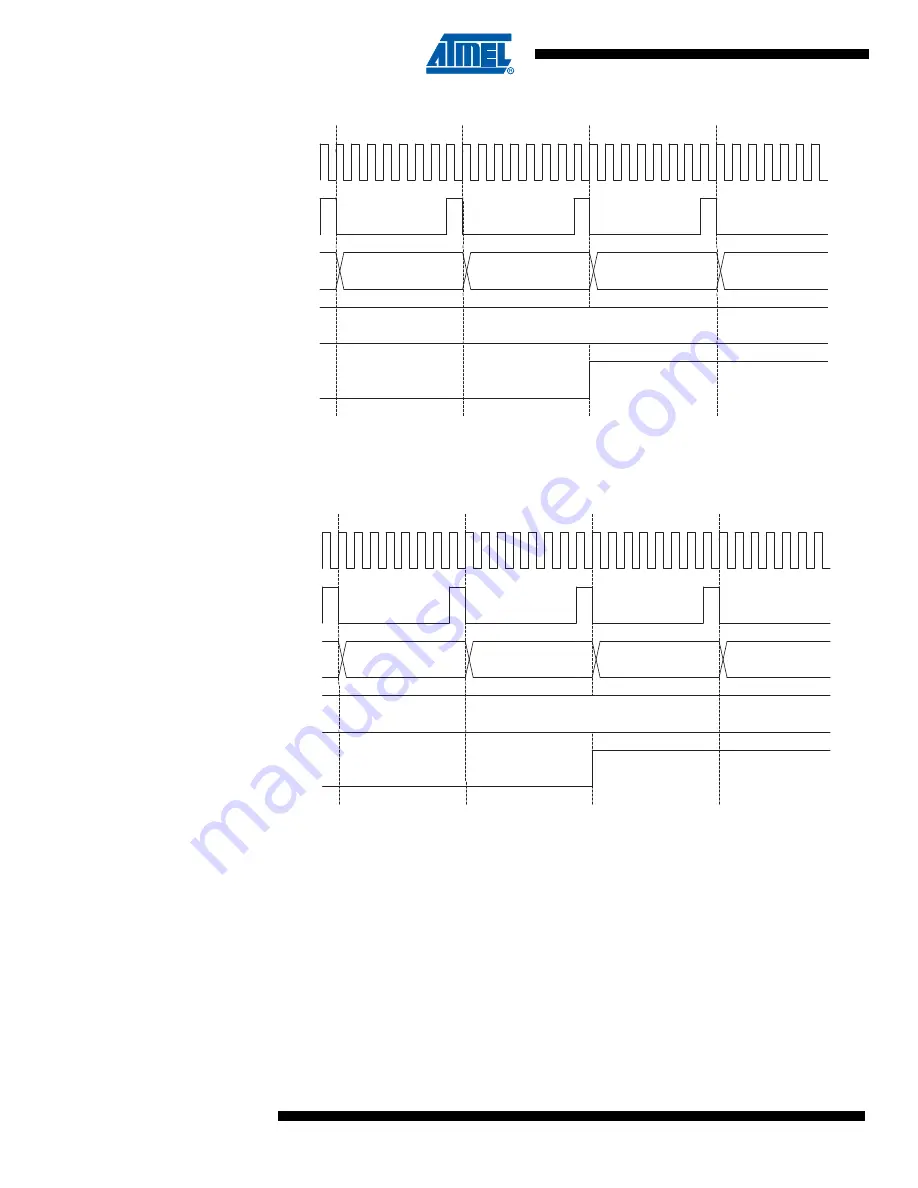

Figure 70.

Timer/Counter Timing Diagram, Setting of OCF2, with Prescaler (f

clk_I/O

/8)

shows the setting of OCF2 and the clearing of TCNT2 in CTC mode.

Figure 71.

Timer/Counter Timing Diagram, Clear Timer on Compare Match Mode, with Pres-

caler (f

clk_I/O

/8)

OCFn

OCRn

TCNTn

OCRn Value

OCRn - 1

OCRn

OCRn + 1

OCRn + 2

clk

I/O

clk

Tn

(clk

I/O

/8)

OCFn

OCRn

TCNTn

(CTC)

TOP

TOP - 1

TOP

BOTTOM

1

clk

I/O

clk

Tn

(clk

I/O

/8)