38

2467S–AVR–07/09

ATmega128

Note:

1. For all fuses “1” means unprogrammed while “0” means programmed.

The various choices for each clocking option is given in the following sections. When the CPU

wakes up from Power-down or Power-save, the selected clock source is used to time the start-

up, ensuring stable Oscillator operation before instruction execution starts. When the CPU starts

from reset, there is as an additional delay allowing the power to reach a stable level before com-

mencing normal operation. The Watchdog Oscillator is used for timing this real-time part of the

start-up time. The number of WDT Oscillator cycles used for each time-out is shown in

The frequency of the Watchdog Oscillator is voltage dependent as shown in the

Default Clock

Source

The device is shipped with CKSEL = “0001” and SUT = “10”. The default clock source setting is

therefore the Internal RC Oscillator with longest startup time. This default setting ensures that all

users can make their desired clock source setting using an In-System or Parallel Programmer.

External RC Oscillator

1000 - 0101

Calibrated Internal RC Oscillator

0100 - 0001

External Clock

0000

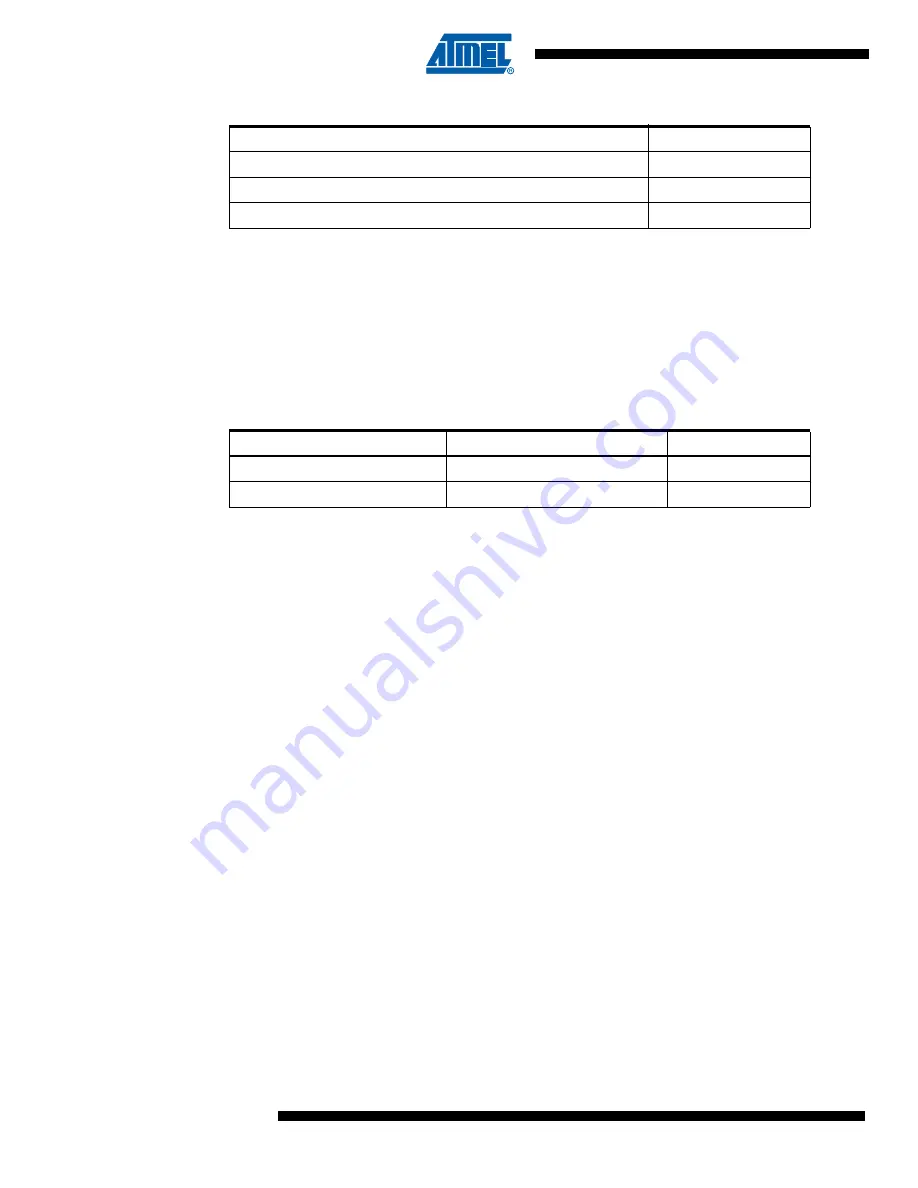

Table 7.

Number of Watchdog Oscillator Cycles

Typical Time-out (V

CC

= 5.0V)

Typical Time-Out (V

CC

= 3.0V)

Number of Cycles

4.1 ms

4.3 ms

4K (4,096)

65 ms

69 ms

64K (65,536)

Table 6.

Device Clocking Options Select

Device Clocking Option

CKSEL3..0

(1)