107

ATmega103(L)

0945G–09/01

Parallel Programming

Characteristics

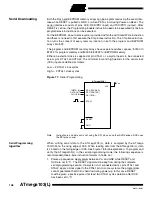

Figure 76.

Parallel Programming Timing

Notes:

1. Use t

WLWH_CE

for Chip Erase and t

WLWH_PFB

for programming the fuse bits.

2. If t

WLWH

is held longer than t

WLRH

, no RDY/BSY pulse will be seen.

Table 41.

Parallel Programming Characteristics T

A

= 25

°

C ± 10%, V

CC

= 5V ± 10%

Symbol

Parameter

Min

Typ

Max

Units

V

PP

Programming Enable Voltage

11.5

12.5

V

I

PP

Programming Enable Current

250

µA

t

DVXH

Data and Control Valid before XTAL1 High

67

ns

t

XHXL

XTAL1 Pulse Width High

67

ns

t

XLDX

Data and Control Hold after XTAL1 Low

67

ns

t

XLWL

XTAL1 Low to WR Low

67

ns

t

BVXH

BS1 Valid before XTAL1 High

67

ns

t

PHPL

PAGEL Pulse Width High

67

ns

t

PLBX

BS1 Hold after PAGEL Low

67

ns

t

PLWL

PAGEL Low to WR Low

67

ns

t

BVWL

BS1 Valid to WR Low

67

ns

t

RHBX

BS1 Hold after RDY/BSY High

67

ns

t

WLWH

WR Pulse Width Low

67

ns

t

WHRL

WR High to RDY/BSY Low

20

ns

t

WLRH

WR Low to RDY/BSY High

0.5

0.7

0.9

ms

t

XLOL

XTAL1 Low to OE Low

67

ns

t

OLDV

OE Low to DATA Valid

20

ns

t

OHDZ

OE High to DATA Tri-stated

20

ns

t

WLWH_CE

WR Pulse Width Low for Chip Erase

5

10

15

ms

t

WLWH_PFB

WR Pulse Width Low for Progr. the Fuse Bits

1.0

1.5

1.8

ms

Data & Contol

(DATA, XA0/1, BS1)

DATA

W

rite

Read

XTAL1

t

XHXL

t

WLWH

t

DVXH

t

XLOL

t

OLDV

t

XLDX

t

PLWL

t

WHRL

t

WLRH

WR

RDY/BSY

OE

PAGEL

t

PHPL

t

PLBX

t

BVXH

t

XLWL

t

RHBX

t

OHDZ

t

BVWL