101

ATmega103(L)

0945G–09/01

.

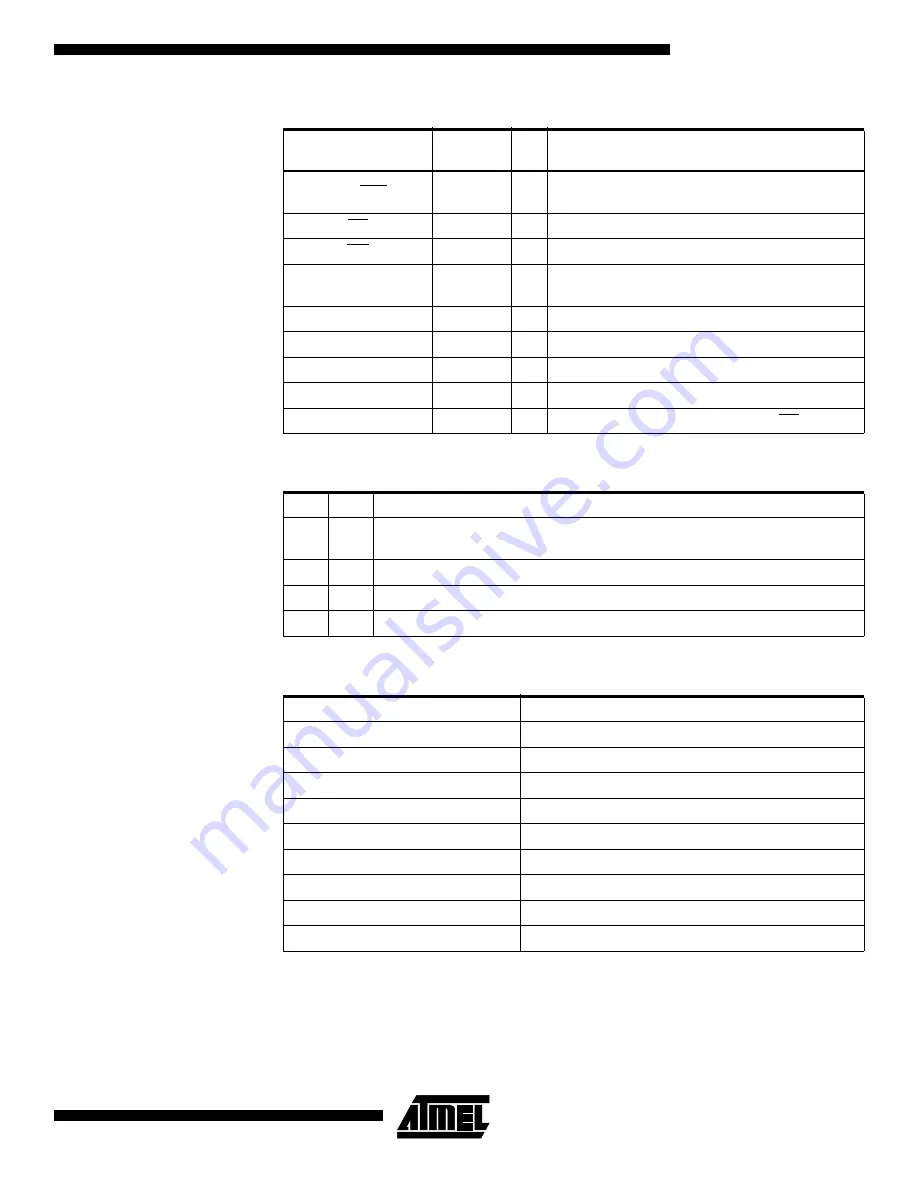

Table 37.

Pin Name Mapping

Signal Name in

Programming Mode

Pin Name

I/O

Function

RDY/BSY

PD1

O

0: Device is busy programming, 1: Device is ready

for new command

OE

PD2

I

Output Enable (active low)

WR

PD3

I

Write Pulse (active low)

BS1

PD4

I

Byte Select 1 (“0” selects low byte, “1” selects

high byte)

XA0

PD5

I

XTAL Action Bit 0

XA1

PD6

I

XTAL Action Bit 1

BS2

PD7

I

Byte Select 2 (always low)

PAGEL

PA0

I

Program Memory Page Load

DATA

PB7-0

I/O

Bi-directional Data Bus (output when OE is low)

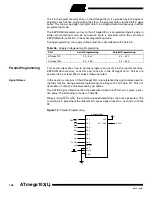

Table 38.

XA1 and XA0 Coding

XA1

XA0

Action when XTAL1 is Pulsed

0

0

Load Flash or EEPROM Address (High or low address byte determined by

BS1)

0

1

Load Data (High or low data byte for Flash determined by BS1)

1

0

Load Command

1

1

No Action, Idle

Table 39.

Command Byte Bit Coding

Command Byte

Command Executed

1000 0000

Chip Erase

0100 0000

Write Fuse Bits

0010 0000

Write Lock Bits

0001 0000

Write Flash

0001 0001

Write EEPROM

0000 1000

Read Signature Bytes

0000 0100

Read Lock and Fuse Bits

0000 0010

Read Flash

0000 0011

Read EEPROM