117

ATmega103(L)

0945G–09/01

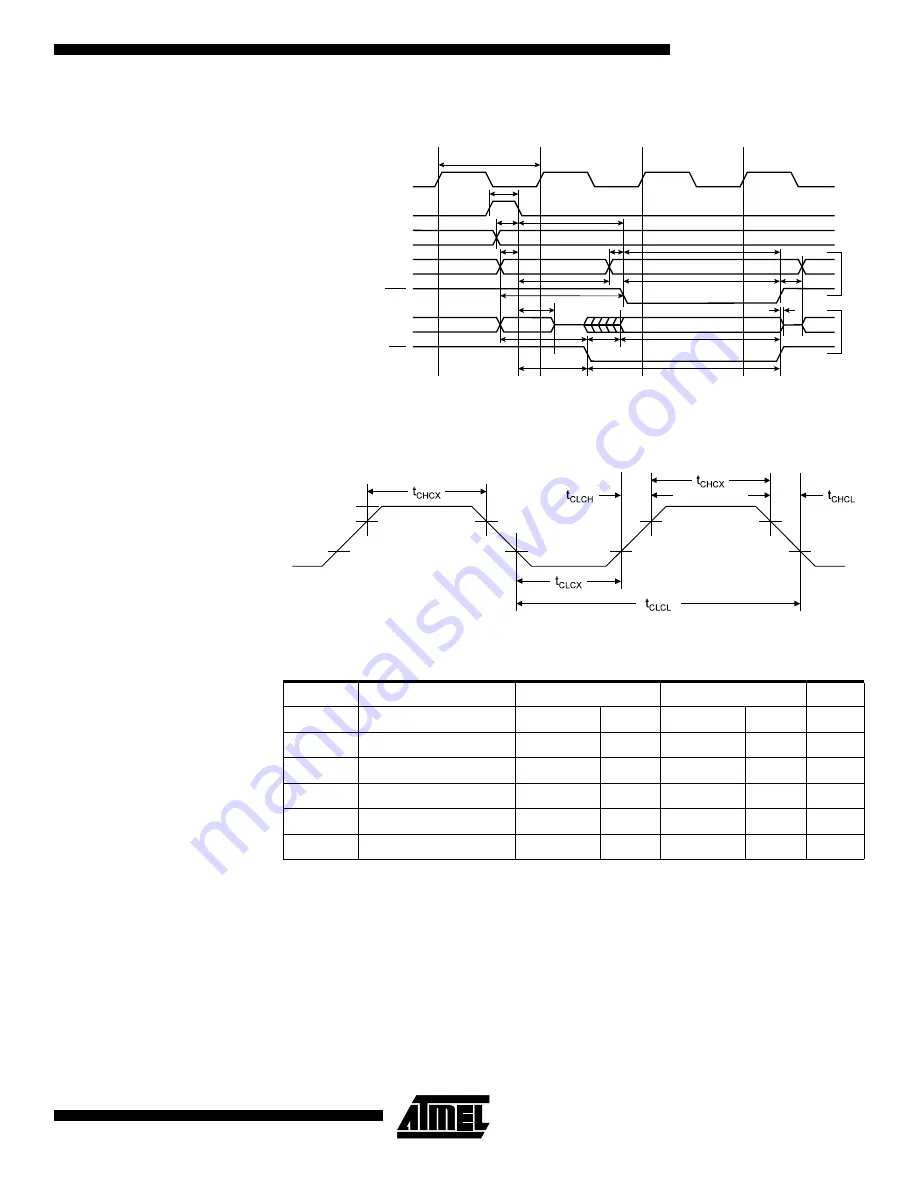

Figure 79.

External RAM Timing

External Clock Drive

Waveforms

Figure 80.

External Clock Drive Waveforms

Note:

See “External Data Memory Timing” on page 115. for a description of how the duty cycle

influences the timing for the external data memory.

System Clock Ø

ALE

WR

RD

Data / Address [7..0]

Data / Address [7..0]

Address [15..8]

Address

Address

Address

T1

T2

T3

T4

Prev. Address

Prev. Address

Prev. Address

1

0

4

2

13

3a

5

Note: Clock cycle T3 is only present when external SRAM Wait State is enabled.

10

12

14

15

11

8

9

16

7

6

3b

Data

Data

Wr

ite

Read

Addr.

Addr.

Table 49.

External Clock Drive

Symbol

Parameter

V

CC

= 2.7V to 3.6V

V

CC

= 4.0V to 5.5V

Units

1/t

CLCL

Oscillator Frequency

0.0

4.0

0.0

6.0

MHz

t

CLCL

Clock Period

250.0

167.0

ns

t

CHCX

High Time

100.0

67.0

ns

t

CLCX

Low Time

100.0

67.0

ns

t

CLCH

Rise Time

1.6

0.5

µs

t

CHCL

Fall Time

1.6

0.5

µs

VIL1

VIH1