72

ATmega103(L)

0945G–09/01

Analog-to-Digital

Converter

Feature list:

•

10-bit Resolution

•

±2 LSB Absolute Accuracy

•

0.5 LSB Integral Non-linearity

•

70 - 280 µs Conversion Time

•

Up to 14 kSPS

•

8 Multiplexed Input Channels

•

Interrupt on ADC Conversion Complete

•

Sleep Mode Noise Canceler

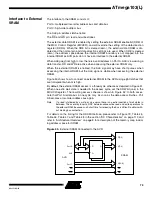

The ATmega103(L) features a 10-bit successive approximation ADC. The ADC is con-

nected to an 8-channel Analog Multiplexer, which allows each pin of Port F to be used

as an input for the ADC. The ADC contains a Sample and Hold Amplifier, which ensures

that the input voltage to the ADC is held at a constant level during conversion. A block

diagram of the ADC is shown in Figure 45.

The ADC has two separate analog supply voltage pins, AV

CC

and AGND. AGND must

be connected to GND, and the voltage on AV

CC

must not differ more than

±

0.3V from

V

CC

. See the section “ADC Noise Canceling Techniques” on page 77 on how to connect

these pins.

An external reference voltage must be applied to the AREF pin. This voltage must be in

the range AGND - AV

CC

.

Figure 45.

Analog-to-Digital Converter Block Schematic

ADC CONVERSION

COMPLETE IRQ

8-BIT DATA BUS

9

0

ADC MULTIPLEXER

SELECT (ADMUX)

ADC CTRL & STATUS

REGISTER (ADCSR)

ADC DATA REGISTER

(ADCH/ADCL)

MUX2

ADIE

ADIE

ADSC

ADEN

ADIF

ADIF

MUX1

MUX0

ADPS0

ADPS1

ADPS2

8-

CHANNEL

MUX

CONVERSION LOGIC

10-BIT DAC

+

-

SAMPLE & HOLD

COMPARATOR

Analog

Inputs

External

Reference

Voltage