29

ATtiny22/22L

•

Bit 4 - WDTOE: Watch Dog Turn-Off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware

will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

•

Bit 3 - WDE: Watch Dog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function

is disabled. WDE can only be cleared if the WDTOE bit is set(one). To disable an enabled watchdog timer, the following

procedure must be followed:

1.

In the same operation, write a logical one to WDTOE and WDE. A logical one must be written to WDE even though

it is set to one before the disable operation starts.

2.

Within the next four clock cycles, write a logical 0 to WDE. This disables the watchdog.

•

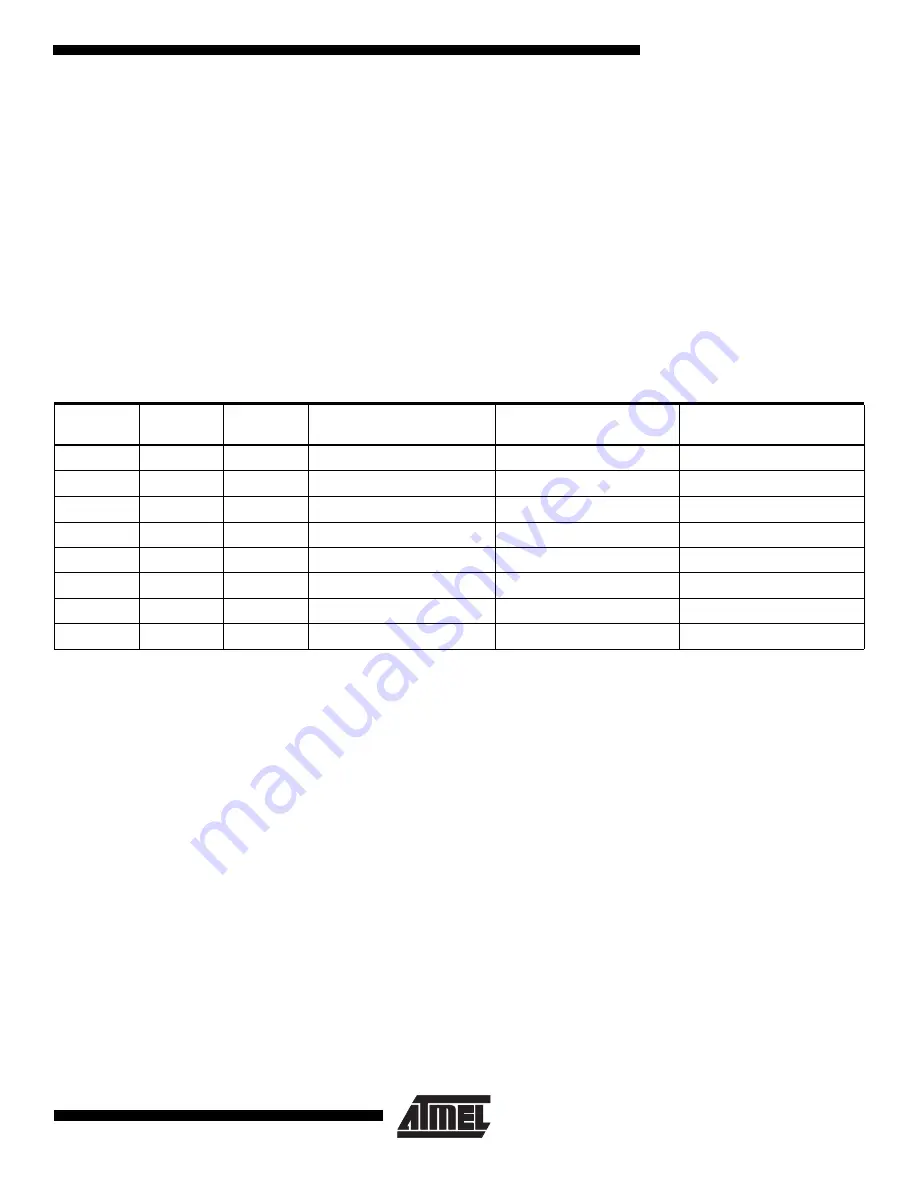

Bits 2..0 - WDP2, WDP1, WDP0: Watchdog Timer Prescaler 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The

different prescaling values and their corresponding time-out periods are shown in Table 9.

Note:

The frequency of the watchdog oscillator is voltage dependent as shown in the Electrical Characteristics section.

The WDR - Watchdog Reset - instruction should always be executed before the Watchdog Timer is enabled. This ensures that

the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without

reset, the watchdog timer may not start to count from zero.

Table 9. Watch Dog Timer Prescale Select

WDP2

WDP1

WDP0

Number of WDT

Oscillator cycles

Typical time-out

at V

CC

= 3.0V

Typical time-out

at V

CC

= 5.0V

0

0

0

16K cycles

47 ms

15 ms

0

0

1

32K cycles

94 ms

30 ms

0

1

0

64K cycles

0.19 s

60 ms

0

1

1

128K cycles

0.38 s

0.12 s

1

0

0

256K cycles

0.75 s

0.24 s

1

0

1

512K cycles

1.5 s

0.49 s

1

1

0

1,024K cycles

3.0 s

0.97 s

1

1

1

2,048K cycles

6.0 s

1.9 s