30-Oct-2020, Rev. 1.1

20

2.6.1

XADC alternate GPIO function

If the XADC function is not desired, the port can be used for additional GPIO expansion

as necessary. However, care must be taken to ensure the appropriate logic voltage

levels are observed when using these signals. VCCIO_35 sets the acceptable voltage

levels for the XADC_GIOx signals. For AD*_P/N signals must be limited to 1.8V logic

levels.

The following signals can be used to perform digital GPIO functionality:

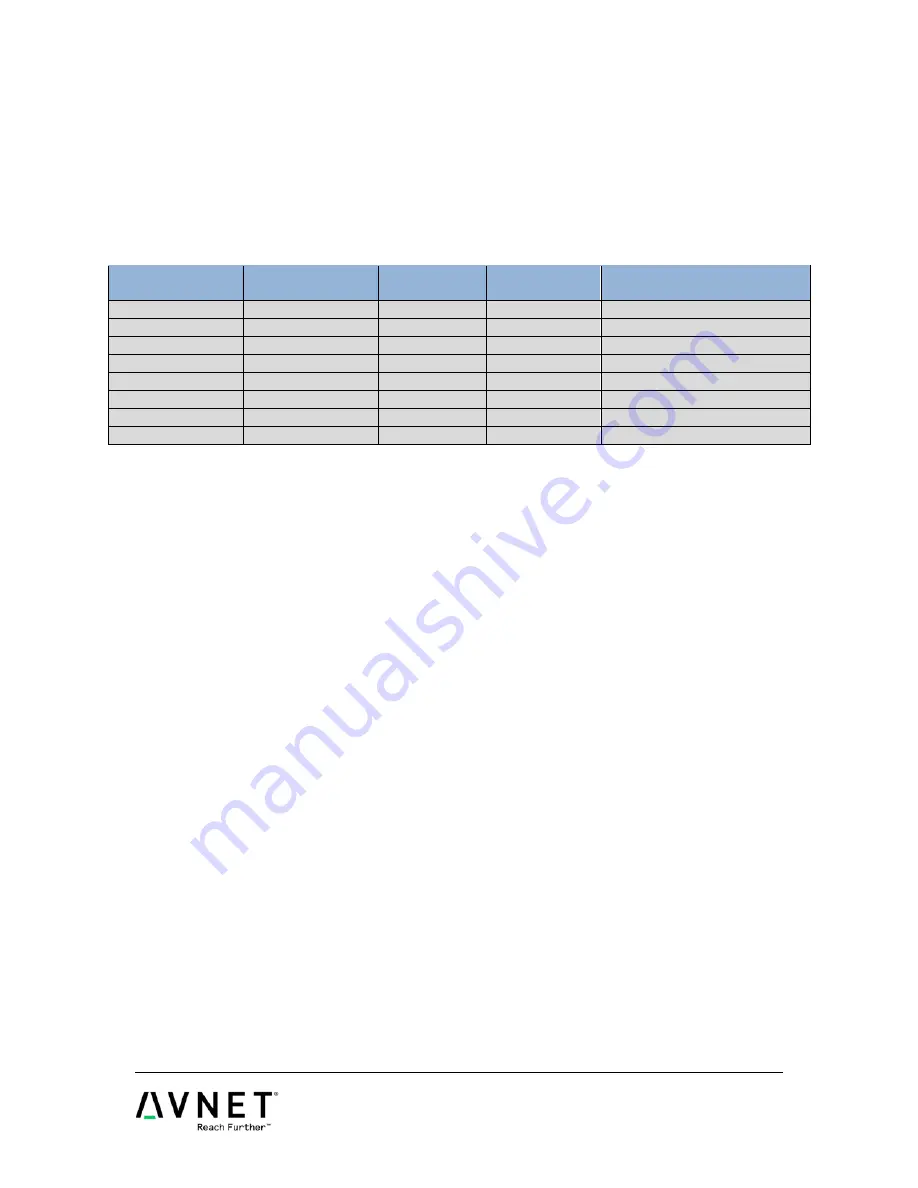

Table 15 - XADC alternate GPIO table

Carrier

Connection

Carrier

Net Name

MicroHeader

Connection

Zynq AP SOC

Connection

Zynq AP SOC Pin

XADC, pin 3

XADC_AD0_P

JX2, pin 17

Bank 35, C20

IO_L1P_T0_AD0P_35

XADC, pin 4

XADC_AD0_N

JX2, pin 19

Bank 35, B20

IO_L1N_T0_AD0N_35

XADC, pin 3

XADC_AD0_P

JX2, pin 18

Bank 35, B19

IO_L1P_T0_AD8P_35

XADC, pin 4

XADC_AD0_N

JX2, pin 20

Bank 35, A20

IO_L1N_T0_AD8N_35

XADC, pin 17

XADC_GIO1

JX2, pin 13

Bank 35, G14

IO_0_35

XADC, pin 18

XADC_GIO0

JX2, pin 47

Bank 35, L16

IO_L11P_T1_SRCC_35

XADC, pin 19

XADC_GIO3

JX2, pin 49

Bank 35, L17

IO_L11N_T1_SRCC_35

XADC, pin 20

XADC_GIO2

JX2, pin 14

Bank 35, J15

IO_25_35