30-Oct-2020, Rev. 1.1

24

2.8.2

Voltage Regulators

The following table lists the power solution for the IO Carrier Card. Two rails are

independent and adjustable supplying power to the Zynq PL I/O banks and connected

Pmods™. VCCio_35 drives banks 35 and 13 (if 7Z020 is populated on MicroZed) as

well as 5 Pmod™ connectors.

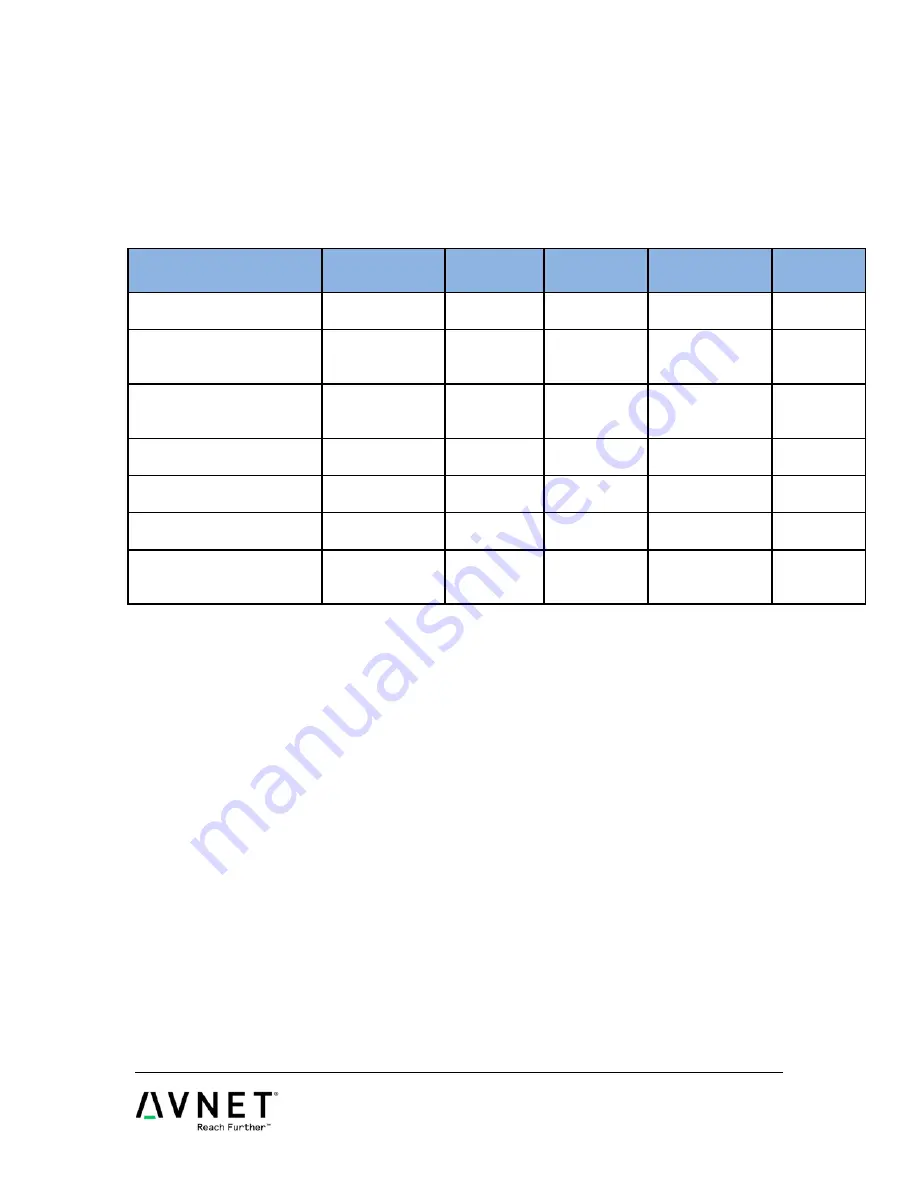

The table below shows the minimum required voltage rails, currents, and tolerances.

Table 20 – Voltage Rails w/ Current Estimates

Voltage (V)

7Z010

Current

7Z020

Current

Tolerance

IC

Notes

Vin (MicroZed Module)

5W

6.5W

5.00%

N/A

Filtered from

Vin, J4.3

Vadj (VCCio_34) – 1.8V,

2.5V or 3.3V

2.3A @ 3.3V

2.3A @ 3.3V

5.00%

REG3,

MAX15066

Pmods +

VCCio

Banks, TP8

Vadj (VCCio_35) – 1.8V,

2.5V or 3.3V

<2.0A @ 3.3V

2.85A @ 3.3V

5.00%

REG4,

MAX15066

Pmods +

VCCio

Banks, TP9

1.8 (analog/Vccadc)

150 mA

150 mA

5.00%

REG1, MAX8891-

18

Filtered from

Vin, TP6

1.25V (analog/Vref)

50 mA

50 mA

0.2%

REG2,

MAX6037A-12

Filtered from

Vin, TP7

3.3V Main

490 mA

500 mA

5.00%

REG5,

MAX17

Filtered from

Vin, TP10

5.0V (analog/AMS)

0.15A

0.15A

5.00%

N/A

Filtered from

Vin, Top of

C36

2.8.3

Sequencing

•

PWR_EN signal, active high, JX1.5, allows the carrier to turn on or off the

MicroZed power supplies. R81 and C93 have been placed to facilitate the

timing of this signal during power off conditions. This signal should not be de-

asserted until VCCIO_EN is de-asserted. In the carrier off condition (power

plug removed or power switch turned off), this signal is driven low by the carrier

board.

•

VCCIO_EN signal, active high, JX2.10, originates on the microZed and is the

output of the 1.8V regulator, PG_1V8. This signal enables the carrier’s 3.3V

supply, which in turn enables both VCCIO_34 and VCCIO_13/35. When the

carrier is turned off (power switch turned off or power plug removed) or the

MicroZed’s PG_1V8 signal is de-asserted VCCI_EN is driven low, which turns

off the IOCC and the MicroZed.

•

PG_CARRIER signal, active high, JX2.11, is pulled up by MicroZed’s +3.3V

PG_MODULE signal. This signal is pulled low by the carrier board or the

MicroZed when either board’s power circuitry is not ‘Good’ yet.

•

The following diagram illustrates the power supply sequencing on power up.

Note Vin and PWR_Enable can come up simultaneously, but shown staggered

as PWR_Enable can come up later.