Page 8

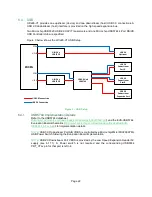

6 Functional Description

The following sections provide brief descriptions of each feature provided on the Ultra96-V1 board.

6.1

Zynq Ult MPSoC

The Zynq Ult MPSoC ZU3EG device (in the SBVA484 package) contains:

•

Processor System (PS):

o

Application Processing Unit

Quad-core ARM Cortex-A53 MPCore with CoreSight; NEON & Single/Double

Precision Floating Point; 32KB/32KB L1 Cache, 1MB L2 Cache

o

Real-Time Processing Unit

Dual-core ARM Cortex-R5 with CoreSight; Single/Double Precision Floating

Point; 32KB/32KB L1 Cache, and TCM

o

Embedded and External Memory

256KB On-Chip Memory w/ECC; External DDR4; DDR3; DDR3L; LPDDR4;

LPDDR3; External Quad-SPI; NAND; eMMC

o

General Connectivity

214 PS I/O; UART; CAN; USB 2.0; I2C; SPI; 32b GPIO; Real Time Clock;

WatchDog Timers; Triple Timer Counters

o

High-Speed Connectivity

4 PS-GTR; PCIe Gen1/2; Serial ATA 3.1; DisplayPort 1.2a; USB 3.0; SGMII

o

Graphic Processing Unit

ARM Mali™-400 MP2; 64KB L2 Cache

•

Programmable Logic (PL)

o

System Logic Cells

154,350

o

CLB Flip-Flops

141,120

o

CLB LUTs

70,560

o

Distributed RAM (Mb) 1.8

o

Block RAM Blocks

216

o

Block RAM (Mb)

7.6

o

UltraRAM Blocks

0

o

UltraRAM (Mb)

0

o

DSP Slices

360

o

CMTs

3

o

System Monitor

2

•

I/O

o

Max PS MIO

78

MIO = multiplexed I/O (up to three banks of 26 I/Os) with support for I/O

voltage of 1.8V or 3.3V

o

Max. PS Transceiver I/O

4 transmit and 4 receive pairs

o

Max. PL HP I/O

156

HP = High-performance I/O with support for I/O voltage from 1.0V to

1.8V

o

Max. PL HD I/O

96

HD = High-density I/O with support for I/O voltage from 1.2V to 3.3V

o

Max. PL Transceiver I/O

4 transmit and 4 receive pairs