Page 29

8.2

Power Estimation Using XPE

Xilinx Power Estimator (XPE) should be used to generate worst case power estimations. The Xilinx

Power Estimator (XPE) spreadsheet is available on Xilinx’ website that can help you get started

with your own power estimation. Avnet has also provided an example of this spreadsheet filled out

for the Ultra96-V1 under Documentation on the Ultra96-V1 website.

8.3

Power Regulators

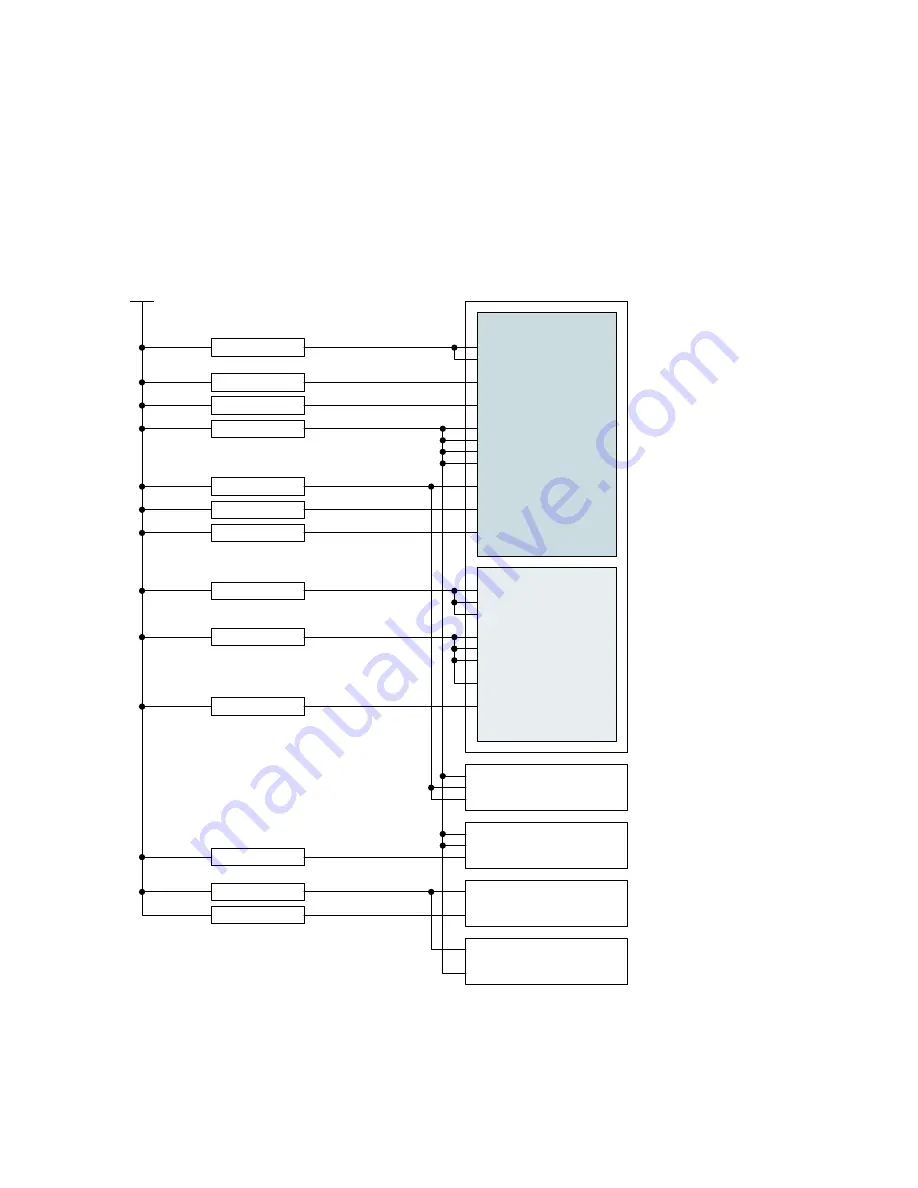

A configurable multi-rail PMIC provides all power for the Ultra96-V1. The power rail configuration

is shown below:

LPDDR4

CH

PS

VCC_PSINTLP

VCC_PSAUX

VCC_PSADC

VCC_PSPLL

VCC_PSINTFP

VCC_PSINTFP_DDR

VCCO_PSIOx

VCCO_PSDDR

VCC_PSDDR_PLL

PS_MGTRAVCC

PS_MGTRAVTT

0.85V, 3.00A, ±5%

VCC_PSINTFP

PL

VCCINT

VCCAUX

VCCAUX_IO

VCCADC

VCCOHD

VCCBRAM

VCCINT_IO

6V-18V

❶

1.80V, 500mA, ±3%

VCC_PSAUX

1.10V, 1.00A, ±5%

VCCO_PSDDR

0.90V, 300mA, ±3%

MGTRAVCC

1.80V, 50mA, ±3%

MGTRAVTT

0.85V, 3A, ±5%

1.80V, 500mA, ±5%

VCCAUX

VCCINT

VCCOHP

1.20V, 100mA, ±5%

VCCO_HP

VDD1

VDD2

VDDQ

5.00V, 3.00A, ±5%

1.25V, 1.00A, ±5%

❶

❸

↓

❷

↓

❶

↓

❶

↓

❷

❸

❷

❸

VCC_5V0

1.20V, 100mA, ±3%

VCC_PSPLL

❷

0.85V, 300mA, ±5%

VCC_PSINTLP

❶

❶

,

❷

,

❸

:

PS Rail Sequence

❶

,

❷

,

❸

:

PL Rail Sequence

↓

:

GPIO Enable req’d

USB3320

ULPI PHY

VDD18

VDDIO

VBUS

❶

3.30V, 1.00A, ±5%

VCC_3V3

VCC_1V2

Wi-Fi/BT

WL18xxMOD

VBAT

VIO

USB5533b

USB3.0 Hub

VDD33

VDD12

Figure 8 – Power Regulation