1

1

2

2

3

3

4

4

5

5

6

6

D

D

C

C

B

B

A

A

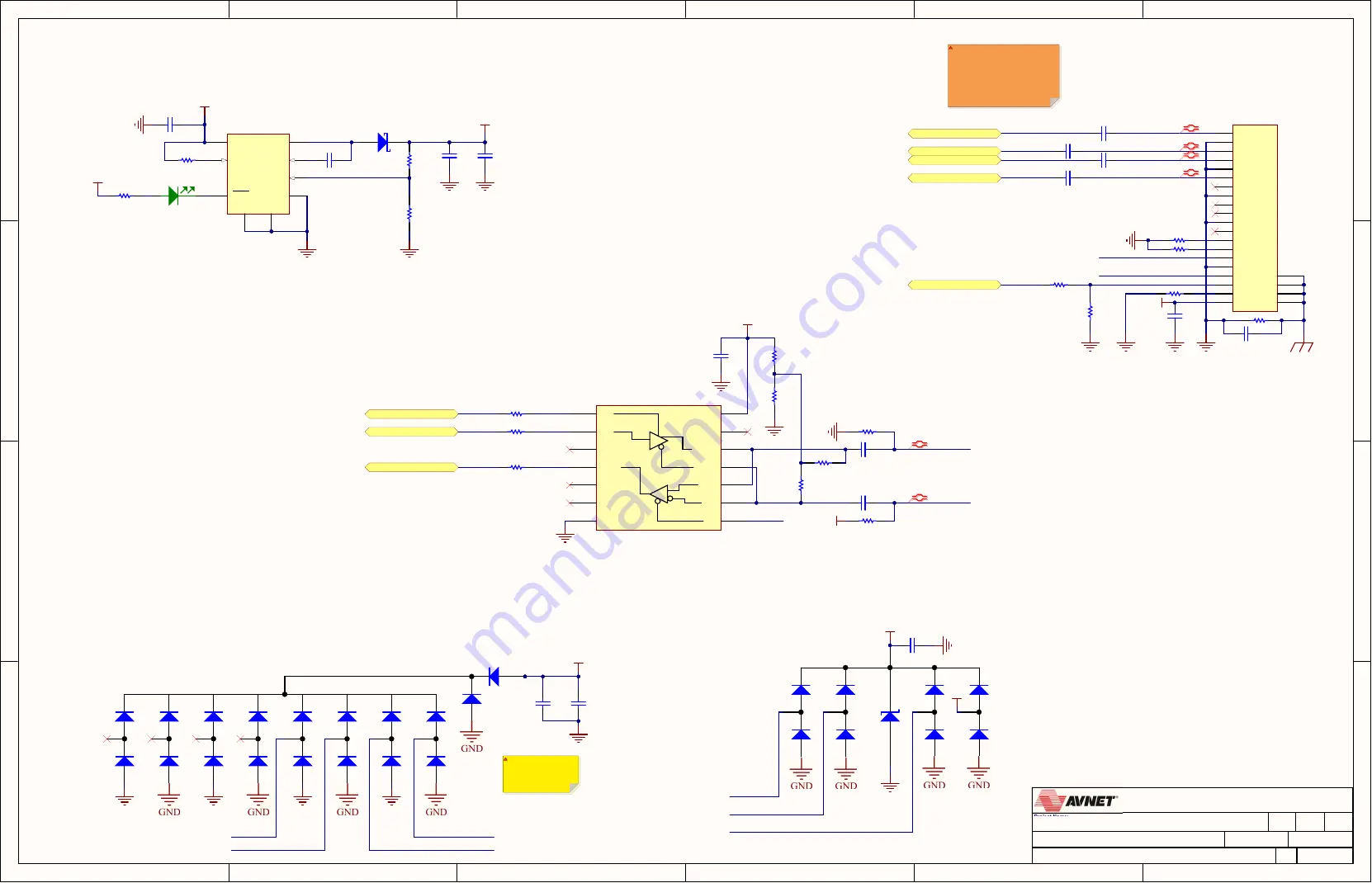

TPD8S009DSMR

D4

0472720001

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

P2

MAX8T

U3

MBRS240LT3G

D2

FIN1019MTCX

U4

DISPLAY PORT INTERFACE

C13

10uF

Avnet Engineering Services

Project Name:

Size:

PCB Rev:

Sheet Title:

Date:

Sheet:

of

11/9/2016

3

SCH-US1CAR

1

02

Variant:

17

Doc Num:

03 - Display Port.SchDoc

B

UltraZed IO Carrier Card

Time:

1:51:52 PM

BOM:

01

GND

+5.0V

D3

240

R15

+3.3V

+3.3V

+3.3V

0.1uF

0.1uF

GND

+3.3VDP

GND

GND

SH_GND1

0

DP_TX2_P

DP_TX2_N

DP_TX3_P

DP_TX3_N

DP_TX3_P

DP_TX3_N

DP_TX2_P

DP_TX2_N

1M

R17

1M

R18

GND

0

R20

GND

DPAUX_C_P

DPAUX_C_N

GND

10

R19

DP_HPD_R

GND

DPAUX_C_P

DPAUX_C_N

DP_HPD_R

MIO_30

10[2C]

MIO_28

10[2C]

MIO_27

10[3C]

MIO_29

10[3C]

+3.3VDP

C14

10uF

GND

GND

GND

4.02K

R16

18.2K

R14

GND

1.00K

R13

GND

DISPLAY PORT VREG

100K

R27

100K

R31

+3.3V

GND

+3.3V

0.1uF

49.9

R28

GND

2.49K

R23

1.50K

R24

GND

GND

DPAUX_C_P

DPAUX_C_N

0

R29

0

R25

0

R26

DPAUX GENERATOR

ESD PROTECTION

ESD PROTECTION

DP_RE_N

DISPLAY PORT CONNECTOR

GTR_TX3_N

10[2A]

GTR_TX3_P

10[2A]

GTR_TX2_N

10[2B]

GTR_TX2_P

10[2B]

(DP_IN)

(DP_OE)

(DP_DOUT)

(DP_HPD)

(DP_TX3P)

(DP_TX3N)

(DP_TX2P)

(DP_TX2N)

Note: dot represents

pins 13 & 15 being

connected.

Layout Note:

All Display Port data signals

(TX_P/N, RX_P/N) routed

to complemented signal @ 100

ohms differentially &

50 ohm single ended.