X20 system modules • X20 electronics module communication • X20CS1070

X20 system User's Manual 3.10

1643

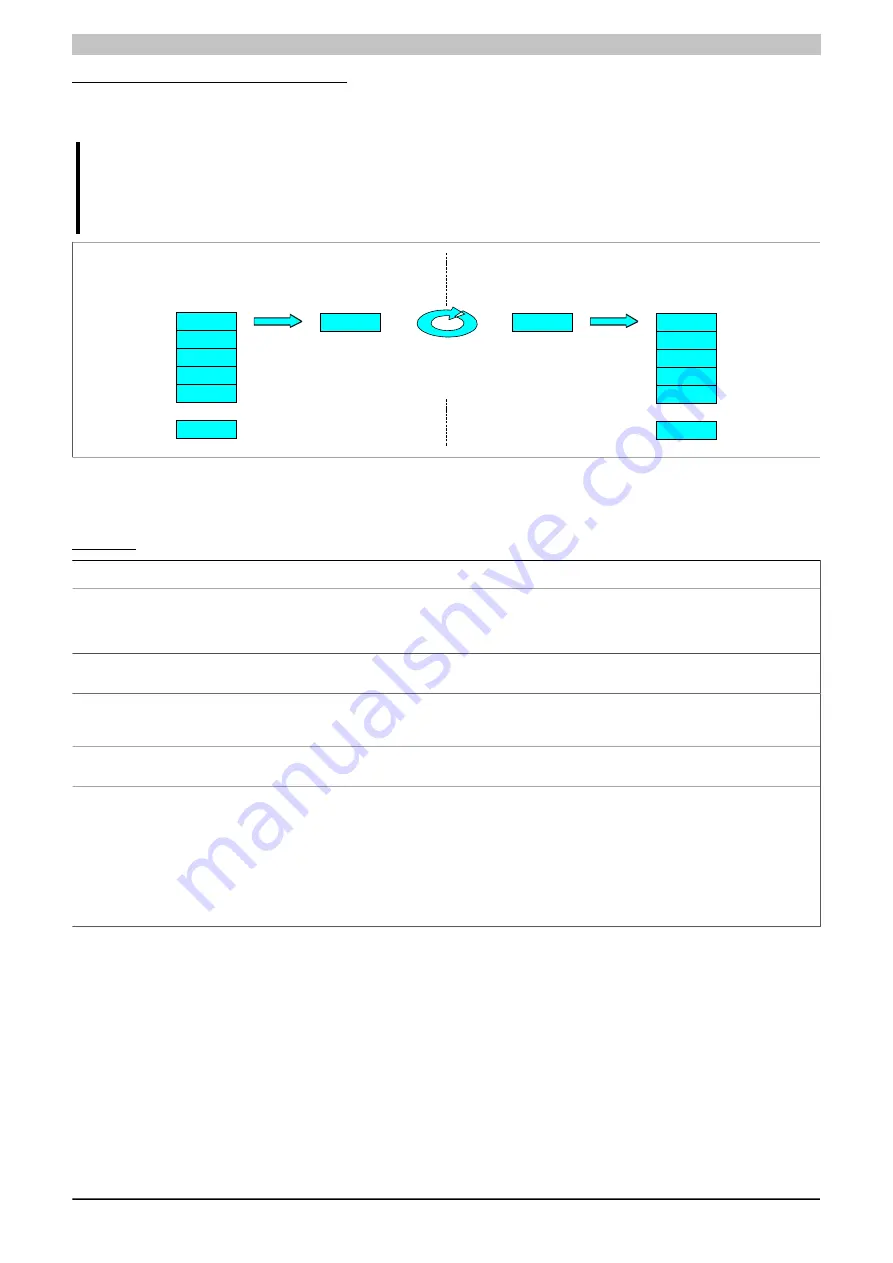

Transmitting data to a module (output)

When transmitting data, the transmit array must be generated in the application program. Sequences are then

transmitted one by one using FlatStream and received by the module.

Information:

Although all B&R modules with FlatStream communication always support the most compact trans-

missions in the output direction, it is recommended to use the same design for the transfer arrays in

both communication directions.

_data_01

_data_02

_data_03

_data_04

_data_05

_data_xx

. . .

TxBytes

When OutputMTU

released:

CPU fills

OutputMTU with

the next sequence

of the transmit array

Transmit array

Type: USINT

OutputMTU

Type: USINT

PLC / Bus controller

The transmit buffer

of the module is

adjusted cyclically to

OutputMTU via X2X

_data_01

_data_02

_data_03

_data_04

_data_05

_data_xx

. . .

*RxBytes

Module adds the transmit buffer

to the internal array

If successful:

InputSequenceAck is

adjusted to the

transmit counter

If the OutputSequence

counter is increased:

Module-internal

receive array

Type: USINT

Module-internal

receive buffer

Type: USINT

Module

Cyc.

Figure 511: FlatStream communication (output)

The length of the message is initially smaller than the OutputMTU. In this case, one sequence would be sufficient

to transmit the entire message and the necessary control byte.

Algorithm

Cyclic status query:

- The Module monitors the OutputSequenceCounter.

0) Cyclic checks:

- The CPU must check OutputSyncAck.

→ If OutputSyncAck = 0: Reset the OutputSyncBit and resynchronize the channel.

- The CPU must check whether OutputMTU is enabled.

→ If OutputSequenceCounter > InputSequenceAck: MTU is not enabled because the last sequence has not yet been acknowledged.

1) Preparation (create transmit array):

- The CPU must split up the message into valid segments and create the necessary control bytes.

- The CPU must add the segments and control bytes to the transmit array.

2) Transmit:

- The CPU transfers the current element of the transmit array to the OutputMTU.

→ The OutputMTU is transferred cyclically to the module's transmit buffer but not processed further.

- The CPU must increase the OutputSequenceCounter.

Response:

- The module accepts the bytes from the internal receive buffer and adds them to the internal receive array.

- The module sends acknowledgment and writes the value of the OutputSequenceCounter to OutputSequenceAck.

3) Completion:

- The CPU must monitor the OutputSequenceAck.

→ A sequence is only considered to have been transmitted successfully if it has been acknowledged via OutputSequenceAck. In order to detect potential trans-

mission errors in the last sequence as well, it is important to make sure that the length of the

Completion

phase is run through long enough.

Note:

To monitor communication times exactly, the task cycles that have passed since the last increase of the OutputSequenceCounter should be counted. In this

way, the number of previous bus cycles necessary for the transmission can be measured. If the monitoring counter exceeds a predefined threshold, then the

sequence can be considered lost.

(The relationship of bus to task cycle can be influenced by the user so that the threshold value needs to be determined individually.)

- Subsequent sequences can only be transmitted in the next bus cycle after the completion check has been carried out successfully.

Summary of Contents for X20 System

Page 2: ......