X90 mobile modules

208

X90 mobile system User's manual V 1.20 - Translation of the original manual

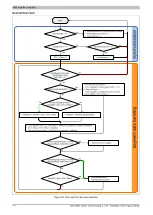

Synchronization

During synchronization, a communication channel is opened. It is important to make sure that a module is present

and that the current value of SequenceCounter is stored on the station receiving the message.

Flatstream can handle full-duplex communication. This means that both channels / communication directions can

be handled separately. They must be synchronized independently so that simplex communication can theoretically

be carried out as well.

Synchronization in the output direction (CPU as the transmitter):

The corresponding synchronization bits (OutputSyncBit and OutputSyncAck) are reset. Because of this, Flatstream

cannot be used at this point in time to transfer messages from the CPU to the module.

Algorithm

1) The CPU must write 000 to OutputSequenceCounter and reset OutputSyncBit.

The CPU must cyclically query the high nibble of register "InputSequence" (checks for 000 in OutputSequenceAck and 0 in OutputSyncAck).

The module does not accept the current contents of InputMTU since the channel is not yet synchronized.

The module matches OutputSequenceAck and OutputSyncAck to the values of OutputSequenceCounter and OutputSyncBit.

2) If the CPU registers the expected values in OutputSequenceAck and OutputSyncAck, it is permitted to increment OutputSequenceCounter.

The CPU continues cyclically querying the high nibble of register "OutputSequence" (checks for 001 in OutputSequenceAck and 0 in InputSyncAck).

The module does not accept the current contents of InputMTU since the channel is not yet synchronized.

The module matches OutputSequenceAck and OutputSyncAck to the values of OutputSequenceCounter and OutputSyncBit.

3) If the CPU registers the expected values in OutputSequenceAck and OutputSyncAck, it is permitted to increment OutputSequenceCounter.

The CPU continues cyclically querying the high nibble of register "OutputSequence" (checks for 001 in OutputSequenceAck and 1 in InputSyncAck).

Note:

Theoretically, data can be transferred from this point forward. However, it is still recommended to wait until the output direction is completely synchronized be-

fore transferring data.

The module sets OutputSyncAck.

The output direction is synchronized, and the CPU can transmit data to the module.

Synchronization in the input direction (CPU as the receiver):

The corresponding synchronization bits (InputSyncBit and InputSyncAck) are reset. Because of this, Flatstream

cannot be used at this point in time to transfer messages from the module to the CPU.

Algorithm

The module writes 000 to InputSequenceCounter and resets InputSyncBit.

The module monitors the high nibble of register "OutputSequence" and expects 000 in InputSequenceAck and 0 in InputSyncAck.

1) The CPU is not permitted to accept the current contents of InputMTU since the channel is not yet synchronized.

The CPU has to match InputSequenceAck and InputSyncAck to the values of InputSequenceCounter and InputSyncBit.

If the module registers the expected values in InputSequenceAck and InputSyncAck, it increments InputSequenceCounter.

The module monitors the high nibble of register "OutputSequence" and expects 001 in InputSequenceAck and 0 in InputSyncAck.

2) The CPU is not permitted to accept the current contents of InputMTU since the channel is not yet synchronized.

The CPU has to match InputSequenceAck and InputSyncAck to the values of InputSequenceCounter and InputSyncBit.

If the module registers the expected values in InputSequenceAck and InputSyncAck, it sets InputSyncBit.

The module monitors the high nibble of register "OutputSequence" and expects 1 in InputSyncAck.

3) The CPU is permitted to set InputSyncAck.

Note:

Theoretically, data could already be transferred in this cycle.

If InputSyncBit is set and InputSequenceCounter has been increased by 1, the values in the enabled Rx bytes must be accepted and acknowledged (see also

"Communication in the input direction").

The input direction is synchronized, and the module can transmit data to the CPU.