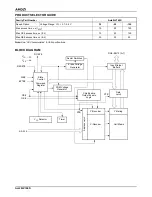

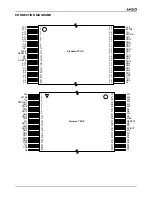

FLI2300 Digital Video Converter Data Sheet

*** Genesis Microchip Confidential ***

PRELIMINARY INFORMATION -- SUBJECT TO CHANGE

1 DESCRIPTION

The FLI2300 is a highly integrated digital video

format converter for CRT-TV applications using

patented deinterlacing and post processing algorithms

from Faroudja Laboratories, coupled with highly

flexible scaling, a wide variety of aspect ratio

conversions, and other special video enhancing

features to produce the highest quality image.

1.1 Inputs

•

Input all industry standard and non-standard

video resolutions, including 480i (NTSC), 576i

(PAL/SECAM), 480p, 720p, 1080i, and VGA to

XGA

•

Digital input, 8-bit Y/Cr/Cb (ITU-R BT656), 8-

bit Y/Pr/Pb, 16-bit Y Cr/Cb (ITU-R BT601), 24-

bit RGB, YCrCb, YPrPb

•

Input pixel rate up to 75MHz maximum

1.2 Outputs

•

Output resolutions include 480p, 576p, 720p,

1080i, 1080p, and VGA to SXGA

•

Interlaced or Progressive output

•

The output can be either analog YUV/RGB

through the integrated 10-bit Digital-To-Analog

Converter (DAC), or digital 24-bit RGB, YCrCb,

YPrPb (4:4:4), or digital 16/20-bit Y Cr/Cb

(4:2:2) Output pixel rate up to 150 MHz

maximum

1.3 Formats

•

Input color manipulation matrix supports all

color spaces: RGB, YPrPb, 4:4:4 YCrCb, 4:2:2

YCr/Cb, ITU-R BT656, ITU-R BT601

•

Output supports analog RGB, YPrPb, and

YCrCb;

•

Output supports digital RGB, YPrPb, 4:4:4

YCrCb and 4:2:2 YCr/Cb

1.4 Frame Rate Conversion

•

Tearless Frame Rate Conversion

50/60/72/75/100/120 Hz

1.5 Front End Processing

•

Motion Adaptive Noise Reduction - Improves

picture quality for off-air material.

•

Cross Color Suppressor (CCS) - Removes cross

color artifacts in composite video signals due to

poor Y/C separation in standard 2-D video

decoders, eliminating the need for expensive 3-D

video decoders.

1.6 Deinterlacing

•

Per-pixel Motion Adaptive Deinterlacing

•

Patented FilmMode Processing - Used for proper

de-interlacing of 3:2 and 2:2 pulldown material.

•

Edit Correction - Film content is continuously

monitored for any break in sequence caused by

“bad edits” and quickly compensates for the

most effective reduction in artifacts.

•

DCDi™ by Faroudja - Video is analyzed on a

single pixel granularity to detect presence or

absence of angled lines and edges, which are

then processed to produce a smooth and natural

looking image without visible artifacts or

“jaggies”.

1.7 Scaling

•

High Quality Fully Programmable Two

Dimensional Scaler

•

Aspect Ratio Conversion for “Anamorphic” or

“Panoramic” (non-linear)

•

Display 4:3 images on 16:9 displays and vice

versa, including Letterbox to Fullscreen,

Pillarbox, and Subtitle Display Modes

•

Pixel and line dropper to generate PIP windows

1.8 TrueLife™

Enhancer

•

Two dimensional, non-linear, luma and chroma

video enhancer brings out details in the picture,

producing a more life-like image.

1.9 Memory

•

32-bit wide SDRAM (i.e. one 2M x 32-bit)

controller, up to 166 MHz operation, for external

SDRAM

Summary of Contents for DV985S

Page 1: ...SERVICE MANUAL DV985S...

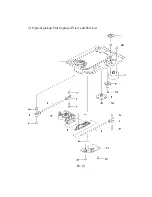

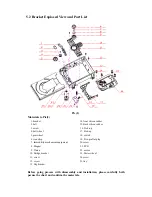

Page 6: ...5 1 Optical pickup Unit Explosed View and Part List Pic 1...

Page 12: ......

Page 47: ......

Page 49: ......

Page 51: ......

Page 53: ......

Page 55: ......

Page 61: ......