Quick Installation Guide

EBC-3615/3615L Quick Installation Guide

17

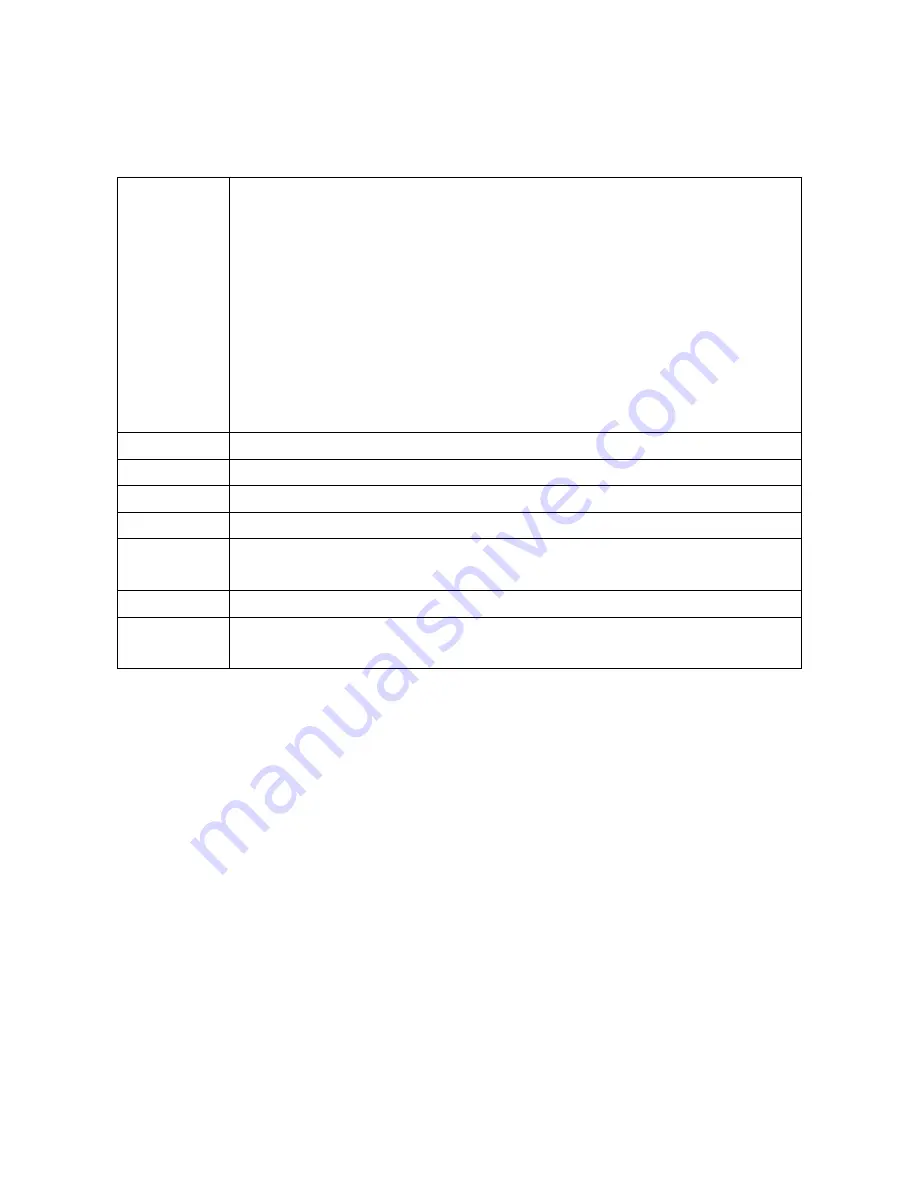

3.2.4 Signal Description – Primary & Secondary LCD Panel Connector (CN4, CN3)

P [47:0]

Flat Panel Data Bit 47 to Bit 0 for single panel implementation.

For Dual Panel Implementation

Panel 1: P21-16, P13-8, P5-0, panel1data

Panel 2: P23, LP2 / HSYNC2

P22, FLM2 / VSYNC2

P15, M2

P47-P24, panel 2 data

Note: P14, P7, P6 are not used for Dual Panel

Implementation. LVDSCLK used as SHFCLK2.

Flat panel data output for 9, 12, 18, 24, 12 x 2, or 18 x 2 bit TFT flat panels. Refer to table

below for configurations for various panel types. The flat panel data and control outputs are

all on-board controlled for secure power-on/off sequencing

SHFCLK

Shift Clock. Pixel clock for flat panel data

LVDSCLK

This pin is used as SHFCLK2 for dual panel configuration

LP

Latch Pulse. Flat panel equivalent of HSYNC (horizontal synchronization)

FLM

First Line Marker. Flat panel equivalent of VSYNC (vertical synchronization)

M

Multipurpose signal, function depends on panel type. May be used as AC drive control

signal or as BLANK# or Display Enable signal

ENBKL

Enable backlight signal. This signal is controlled as a part of the panel power sequencing

ENVEE

Enable VEE. Signal to control the panel power-on/off sequencing. A high level may turn on

the VEE (LCD bias voltage) supply to the panel