IPC@CHIP SC2x3

Hardware Manual V1.02 [01.03.09]

©2000-2009 BECK IPC GmbH

Page 8

3

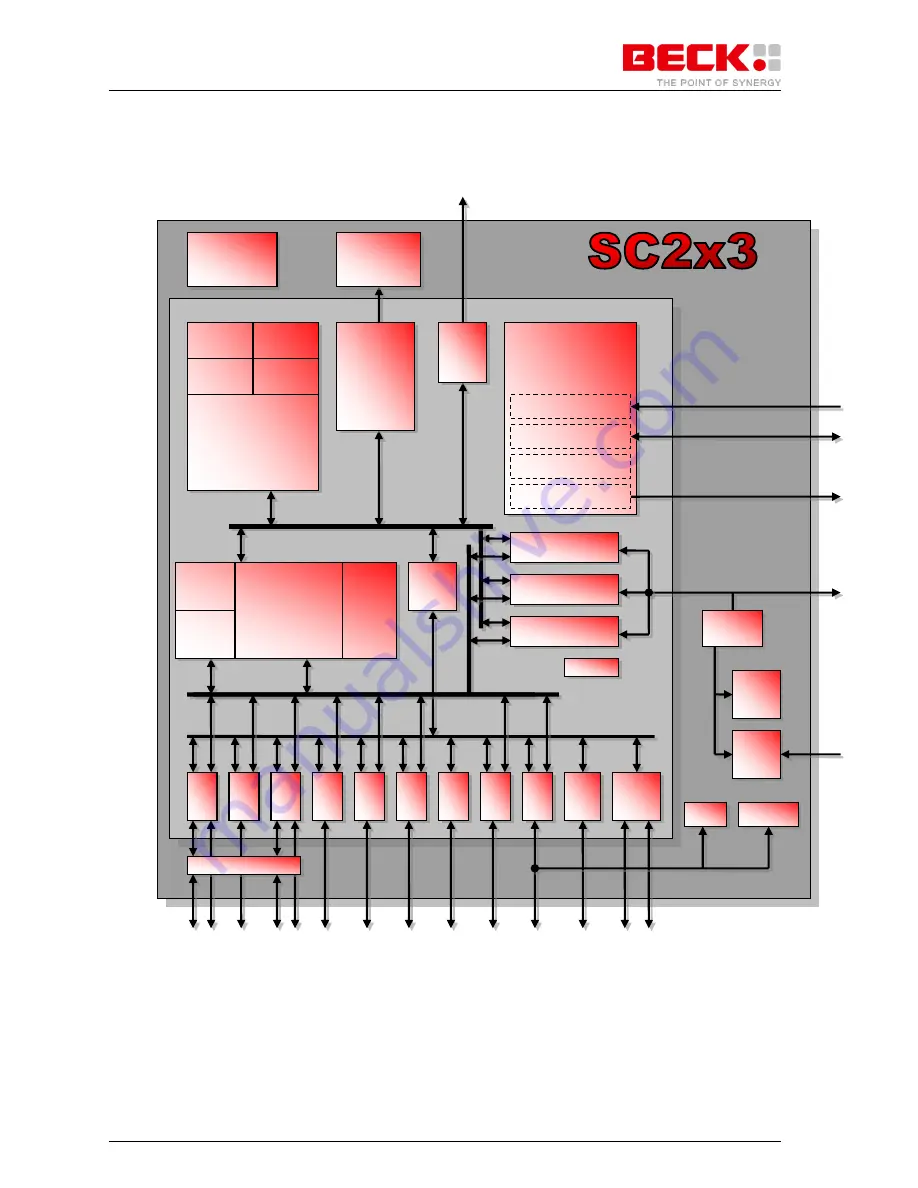

Block Diagram

Figure 3-1: Block Diagram

Embedded

PowerPC 603e

Core

With double

precision FPU

16K

lCache

32 Entry

MMU

16K

DCache

32 Entry

MMU

Systems Integration

Unit

Interrupt Control

System Functions

Real Time Clock

Chip Selects

JTAG

SDRA

M

Mem

ory

Contr

oller

XL Bus

IP Bus

C Bus

SDRAM

Memory

Controller

USB

(two)

BestComm

Intelligent DMA

Unit

Clock/Reset

Generation

GPIO

16K

SRAM

IPBI

PSC1

PSC2

PSC3

PSC4

PSC5

PSC6

SPI

10/100

BaseT

I²C

(two)

J1850

CAN 2.0

A/B

(two)

PCI Controller

SDRAM

Memory

Controller

ROM/SRAM

SDRAM

Memory

Controller

ATA/IDE Host

Controller

SDRAM

Memory

Controller

SDRAM

V24 Transceiver

Power

Supervisory

Circuit

Driver/

Buffer

Flash

SRAM

LM75

E²PROM

Local Plus Bus