58

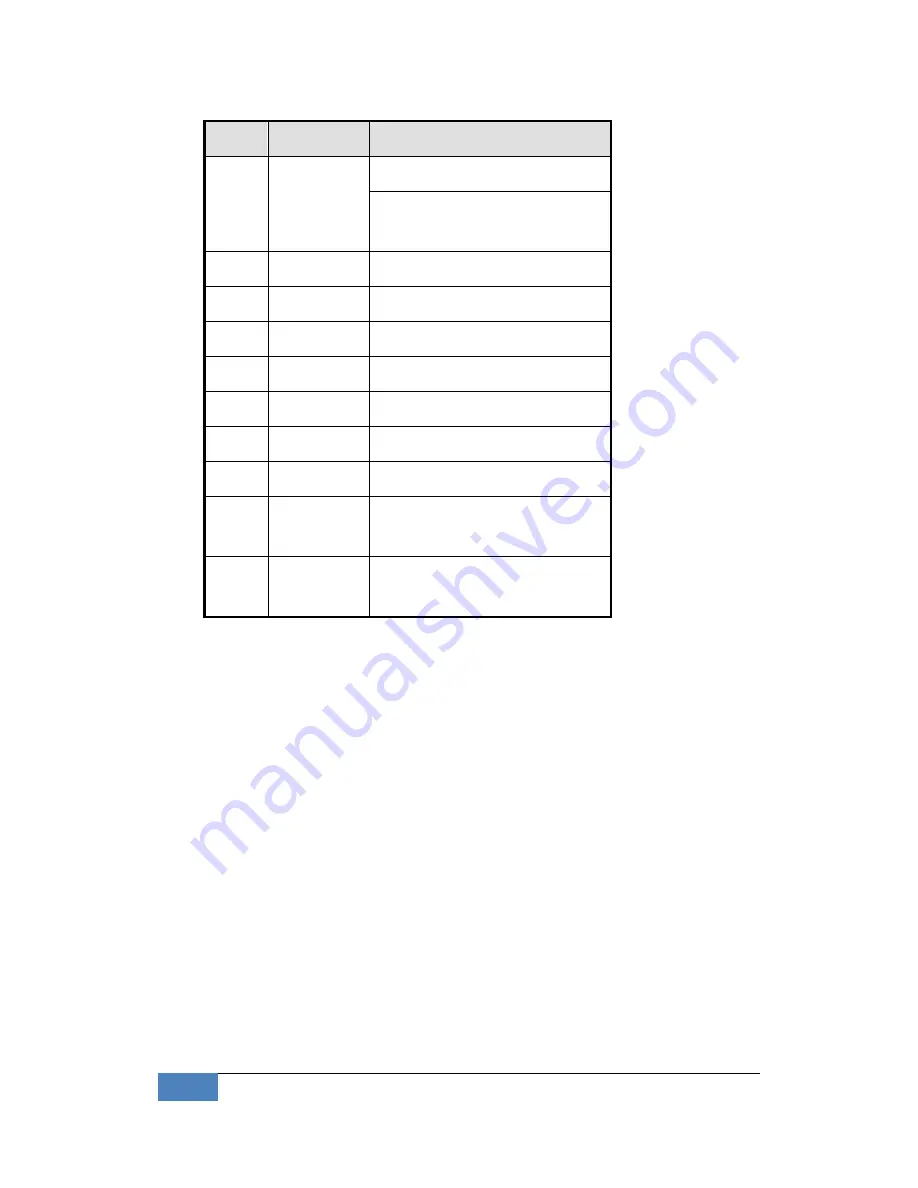

Technical

Reference

|

DLAB

Port

Address

Register

0

Base

+

0

Receiver

buffer

(read)

Transmitter

holding

register

(write)

0

Base

+

1

Interrupt

enable

X

Base

+

2

Interrupt

identification

(read

only)

X

Base

+

3

Line

control

X

Base

+

4

MODEM

control

X

Base

+

5

Line

status

X

Base

+

6

MODEM

status

X

Base

+

7

Scratched

register

1

Base

+

0

Divisor

latch

(least

significant

byte)

1

Base

+

1

Divisor

latch

(most

significant

byte)

6

2

1

Receiver

Buffer

Register

(RBR)

Bit

0

‐

7:

Received

data

byte

(Read

Only)

6

2

2

Transmitter

Holding

Register

(THR)

Bit

0

‐

7:

Transmitter

holding

data

byte

(Write

Only)

6

2

3

Interrupt

Enable

Register

(IER)

Bit

0:

Enable

Received

Data

Available

Interrupt

(ERBFI)

Bit

1:

Enable

Transmitter

Holding

Empty

Interrupt

(ETBEI)

Bit

2:

Enable

Receiver

Line

Status

Interrupt

(ELSI)

Bit

3:

Enable

MODEM

Status

Interrupt

(EDSSI)

Bit

4:

Must

be

0

Bit

5:

Must

be

0