Document type:

Title:

Revision date:

Revision:

User's Manual (MUT)

Mod. V1724 8 Channel 14bit - 100MS/s Digitizer

06/11/2007

7

NPO:

Filename:

Number of pages:

Page:

00103/05:V1724x.MUTx/07 V1724_REV7.DOC

63

54

[5]

Clock source (see § 2.6):

0 = Internal

1 = External

[4]

EVENT FULL: it is set to 1 as the maximum nr. of events to be read

is reached

[3]

EVENT READY: it is set to 1 as at least one event is available to

readout

[2]

0 = RUN off

1 = RUN on

[1] reserved

[0] reserved

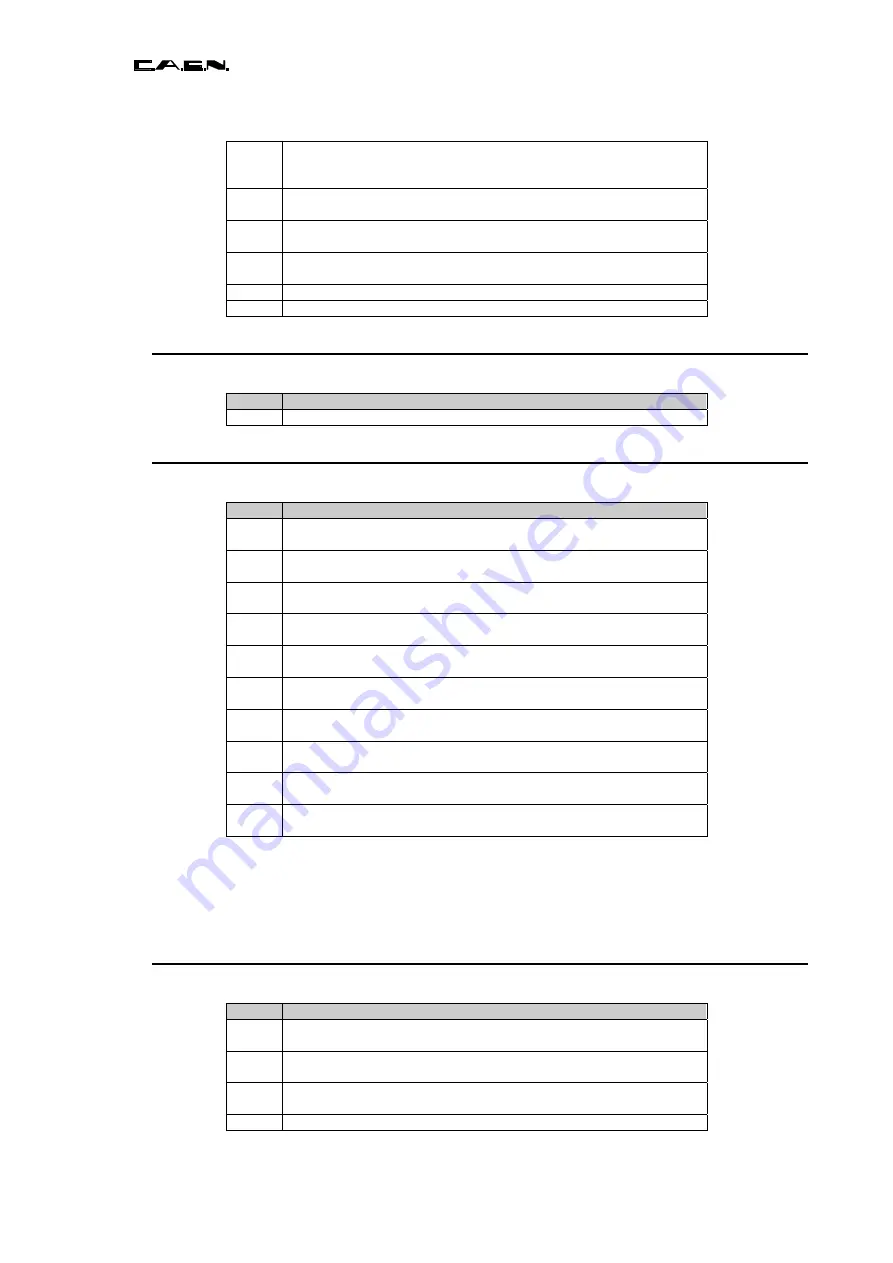

4.20.

Software Trigger (0x8108; w)

Bit

Function

[31:0] A write access to this location generates a trigger via software

4.21.

Trigger Source Enable Mask (0x810C; r/w)

Bit

Function

[31]

0 = Software Trigger Disabled

1 = Software Trigger Enabled

[30]

0 = External Trigger Disabled

1 = External Trigger Enabled

[7]

0 = Channel 7 trigger disabled

1 = Channel 7 trigger enabled

[6]

0 = Channel 6 trigger disabled

1 = Channel 6 trigger enabled

[5]

0 = Channel 5 trigger disabled

1 = Channel 5 trigger enabled

[4]

0 = Channel 4 trigger disabled

1 = Channel 4 trigger enabled

[3]

0 = Channel 3 trigger disabled

1 = Channel 3 trigger enabled

[2]

0 = Channel 2 trigger disabled

1 = Channel 2 trigger enabled

[1]

0 = Channel 1 trigger disabled

1 = Channel 1 trigger enabled

[0]

0 = Channel 0 trigger disabled

1 = Channel 0 trigger enabled

This register bits[0,7] enable the channels to generate a local trigger as the digitised

signal exceeds the Vth threshold (see § 3.5.3). Bit0 enables Ch0 to generate the trigger,

bit1 enables Ch1 to generate the trigger and so on.

EXTERNAL TRIGGER ENABLE (bit30) enables the board to sense TRG-IN signals

SW TRIGGER ENABLE (bit 31) enables the board to sense software trigger (see § 4.20).

4.22.

Front Panel Trigger Out Enable Mask (0x8110; r/w)

Bit

Function

[31]

0 = Software Trigger Disabled

1 = Software Trigger Enabled

[30]

0 = External Trigger Disabled

1 = External Trigger Enabled

[7]

0 = Channel 7 trigger disabled

1 = Channel 7 trigger enabled

[6]

0 = Channel 6 trigger disabled