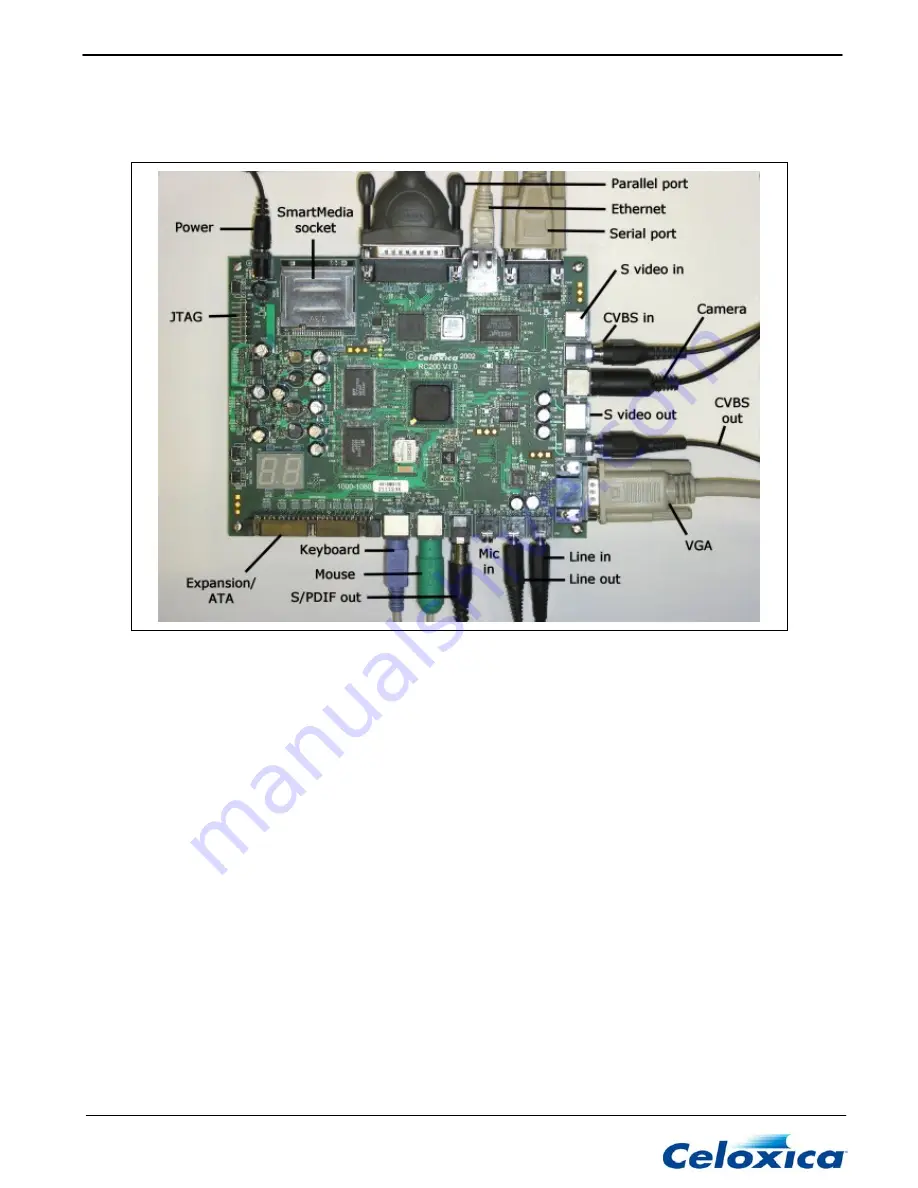

Installation and set-up

4.2 RC200/203 connectors

C

ONNECTORS ON THE

RC200/203

4.3 CPLD

The RC200/203 has a Xilinx XC95144XL 3.3V CPLD.

The CPLD is connected to the:

•

FPGA

•

Parallel

port

•

SmartMedia

Flash

RAM

•

JTAG

chain

The CPLD can configure the FPGA with data received from SmartMedia memory, or via the parallel port.

4.3.1 Control and data pins

The RC200 CPLD has 10 control lines and 8 data lines. 3 of the control lines are used as an address

bus. The control lines have two meanings, depending on the

FPGA operation mode

(see page 19).

The FPGA operation mode is determined by whether the CPLD pin P9 is set high or low.

www.celoxica.com

Page 14