CS42528

34

DS586PP5

4.6.4b

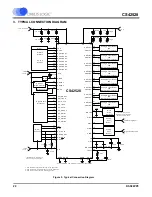

OLM Config #2

This configuration will support up to 8 channels of DAC data, 6 channels of ADC data and no channels of

S/PDIF received data and will handle up to 20-bit samples at a sampling frequency of 96 kHz on all chan-

nels for both the DAC and ADC. The output data stream of the internal and external ADCs is configured

to use the SAI_SDOUT output and run at the SAI_SP clock speeds.

Register / Bit Settings

Description

Functional Mode Register (addr = 03h)

Set CODEC_FMx = SAI_FMx = 00,01,10

CX_LRCK must equal SAI_LRCK; sample rate conversion not supported

Set ADC_SP SELx = 10

Configure ADC data to use SAI_SDOUT and SAI_SP Clocks. S/PDIF data

is not supported in this configuration

Interface Format Register (addr = 04h)

Set DIFx bits to proper serial format

Select the digital interface format when not in one line mode

Set ADC_OLx bits = 00,01,10

Select ADC operating mode, see table below for valid combinations

Set DAC_OLx bits = 00,01

Select DAC operating mode, see table below for valid combinations

Misc. Control Register (addr = 05h)

Set CODEC_SP M/S = 1

Set CODEC Serial Port to master mode.

Set SAI_SP M/S = 1

Set Serial Audio Interface Port to master mode.

Set EXT ADC SCLK = 1

Identify external ADC clock source as CODEC Serial Port.

CX_SDOUT= not used

SAI_SDOUT=ADC Data

DAC Mode

Not One Line Mode

One Line Mode #1

One Line Mode #2

ADC Mode

Not One

Line Mode

CX_SCLK=64 Fs

CX_LRCK=SSM/DSM/QSM

SAI_SCLK=64 Fs

SAI_LRCK=CX_LRCK

CX_SCLK=128 Fs

CX_LRCK=SSM

SAI_SCLK=64 Fs

SAI_LRCK=CX_LRCK

not valid

One Line

Mode #1

CX_SCLK=64 Fs

CX_LRCK=SSM/DSM

SAI_SCLK=128 Fs

SAI_LRCK=CX_LRCK

CX_SCLK=128 Fs

CX_LRCK=SSM

SAI_SCLK=128 Fs

SAI_LRCK=CX_LRCK

not valid

One Line

Mode #2

CX_SCLK=64 Fs

CX_LRCK=SSM

SAI_SCLK=256 Fs

SAI_LRCK=CX_LRCK

not valid

not valid

SCLK_PORT1

LRCK_PORT1

SDIN_PORT1

SCLK_PORT2

LRCK_PORT2

SDIN_PORT2

SCLK_PORT3

LRCK_PORT3

SDOUT1_PORT3

SDOUT2_PORT3

SDOUT3_PORT3

SDOUT4_PORT3

RMCK

ADCIN1

ADCIN2

MCLK

SDOUT1

SDOUT2

LRCK

SCLK

64Fs,128Fs

ADC Data

64Fs,128Fs,

256Fs

DIGITAL AUDIO

PROCESSOR

CS5361

CS5361

SAI_SCLK

SAI_LRCK

SAI_SDOUT

CX_SCLK

CX_LRCK

CX_SDOUT

CX_SDIN1

CX_SDIN2

CX_SDIN3

CX_SDIN4

MCLK

Figure 17. OLM Configuration #2

CS42528