DS586PP5

77

CS42528

11. APPENDIX B: S/PDIF RECEIVER

11.1

Error Reporting and Hold Function

The UNLOCK bit indicates whether the PLL is locked to the incoming S/PDIF data. The V bit reflects the

current validity bit status. The CONF (confidence) bit indicates the amplitude of the eye pattern opening,

indicating a link that is close to generating errors. The BIP (bi-phase) error bit indicates an error in incom-

ing bi-phase coding. The PAR (parity) bit indicates a received parity error.

The error bits are "sticky": they are set on the first occurrence of the associated error and will remain set

until the user reads the register through the control port. This enables the register to log all unmasked

errors that occurred since the last time the register was read.

The Receiver Errors Mask register (See “Receiver Errors Mask (address 27h)” on page 69) allows mask-

ing of individual errors. The bits in this register serve as masks for the corresponding bits of the Receiver

Error Register. If a mask bit is set to 1, the error is unmasked, which implies the following: its occurrence

will be reported in the receiver error register, invoke the occurrence of a RERR interrupt, and affect the

current audio sample according to the status of the HOLD bits. The HOLD bits allow a choice of holding

the previous sample, replacing the current sample with zero (mute), or not changing the current audio

sample. If a mask bit is set to 0, the error is masked, which implies the following: its occurrence will not

be reported in the receiver error register, the RERR interrupt will not be generated, and the current audio

sample will not be affected. The QCRC and CCRC errors do not affect the current audio sample, even if

unmasked.

11.2

Channel Status Data Handling

The setting of the CHS bit in the register “Channel Status Data Buffer Control (address 24h)” on page 66

determines whether the channel status decodes are from the A channel (CHS = 0) or B channel

(CHS = 1).

The PRO (professional) bit is extracted directly. For consumer data, the COPY (copyright) bit is extracted,

and the category code and L bits are decoded to determine SCMS status, indicated by the ORIG (original)

bit. If the category code is set to General on the incoming S/PDIF stream, copyright will always be indi-

cated even when the stream indicates no copyright. Finally, the AUDIO bit is extracted and used to set an

AUDIO indicator, as described in section 4.4.5, Non-Audio Auto-Detection.

If 50/15 µs pre-emphasis is detected, and the Receiver Auto De-emphasis control is enabled, then de-

emphasis will automatically be applied to the incoming digital PCM data. See “Functional Mode (address

03h)” on page 49 for more details.

The encoded channel status bits which indicate sample word length are decoded according to IEC 60958.

Audio data routed to the Serial Audio Interface port is unaffected by the word length settings; all 24 bits

are passed on as received.

The CS42528 also contains sufficient RAM to store a full block of C data for both A and B channels

(192 x 2 = 384 bits), and also 384 bits of User (U data) information. The user may read from these buffer

RAMs through the control port.

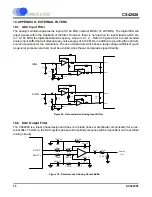

The buffering scheme involves 2 block-sized buffers, named D and E, as shown in Figure 26. The MSB

of each byte represents the first bit in the serial C data stream. For example, the MSB of byte 0 (which is

at control port address 4Ah) is the consumer/professional bit for channel status block A.

The first buffer (D) accepts incoming C data from the S/PDIF receiver. The 2nd buffer (E) accepts entire

blocks of data from the D buffer. The E buffer is also accessible from the control port, allowing reading of

the C data.