46

©

Copyright 2004 Cirrus Logic, Inc.

DS651UM21

Version 2.1

CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

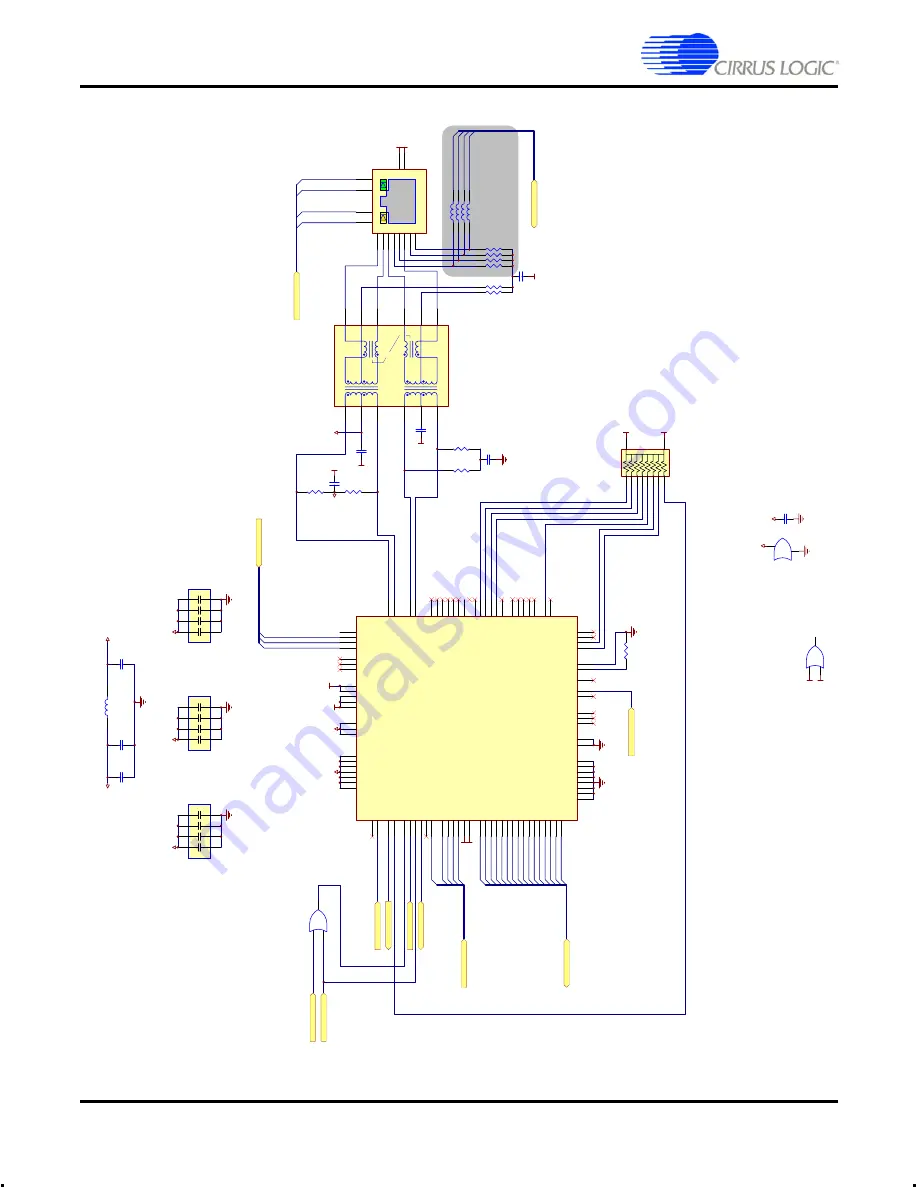

Figure 26. CM-2 RevE Schematic Page 5 of 7

C

irru

s Lo

g

ic,

In

c.

Prim

ary Ethe

r

Tit

le:

IOR#

1

IOW#

2

AE

N

3

IOWA

IT

4

DVDD

5

SD0

6

SD1

7

SD2

8

SD3

9

SD4

10

SD5

11

SD6

12

SD7

13

RST

14

DGND

15

TEST1

16

TEST2

17

TEST3

18

TEST4

19

DVDD

20

X2_25M

21

X1_25M

22

DGND

23

SD

24

BGGND

25

BGRES

26

AVDD

27

AVDD

28

RXI+

29

RXI-

30

AGND

31

AGND

32

TXO+

33

TXO-

34

AVDD

35

DVDD

36

LINK_

I

37

RXD0

38

RXD1

39

RXD2

40

RXD3

41

DGND

42

CRS

43

COL

44

RX_

DV

45

RX_

ER

46

RX_

CLK

47

TEST5

48

TX_

CLK

49

TXD0

50

TXD1

51

TXD2

52

TXD3

53

TX_

EN

54

DVDD

55

MDIO

56

MDC

57

DGND

58

CLK20MO

59

SPEED#

60

DUP#

61

LINKACT#

62

DGND

63

EEDI

64

EEDO

65

EECK

66

EECS

67

GPIO0

68

GPIO1

69

GPIO2

70

GPIO3

71

DVDD

72

DVDD

73

NC

74

NC

75

DGND

76

NC

77

LINK_

O

78

WA

KEU

P

79

PW

_R

S

T

#

80

DGND

81

SD1

5

82

SD1

4

83

SD1

3

84

SD1

2

85

SD1

1

86

SD1

0

87

SD9

88

SD8

89

DVDD

90

IO1

6

91

CMD

92

SA

4

93

SA

5

94

SA

6

95

SA

7

96

SA

8

97

SA

9

98

DGND

99

INT

100

U7

D

M

9000

R2

5

6.8K

O

h

m

, 1%

K

eep

res

clo

se

to

ch

ip

p

in

s.

VCC_

P

HY1

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

A

DDR0

DA

TA

0

DA

TA

1

DA

TA

2

DA

TA

3

DA

TA

4

DA

TA

5

DA

TA

6

DA

TA

7

DA

TA

8

DA

TA

9

DA

TA

1

0

DA

TA

1

1

DA

TA

1

2

DA

TA

1

3

DA

TA

1

4

DA

TA

1

5

A

DDR[

0

..

1

9

]

D

A

T

A

[0..15]

A

DDR[

0

..

1

9

]

D

A

T

A

[0..15]

HRESET_

BU

F#

VCC_

+

3

.3

GND

OE#

WE#

MA

C_

CS#

IOWA

IT

HRESET_

BU

F#

OE#

WE#

MA

C_

CS#

IOWA

IT

MA

C_

IRQ0

MA

C_

IRQ0

A

DDR2

A

DDR3

A

DDR1

A

DDR4

LED_

CTRL[

0

..

2

]

LED_

CTRL[

0

..

2

]

VCC_

+

3

.3

VCC_

P

HY1

C4

6

0.01 uF

FB2

F

B

E

A

D

, 68 O

h

m

@

100 M

H

z

C6

10 uF

, X

5

R

, 6.3 V

o

lt

s

C7

10 uF

, X

5

R

, 6.3 V

o

lt

s

VCC_

+

3

.3

VCC_

P

HY1

1

2

3

4

5

6

7

8

CN8

0.1 uF

, 4x

A

rray

1

2

3

4

5

6

7

8

CN6

0.1 uF

, 4x

A

rray

VCC_

+

3

.3

1

2

3

4

5

6

7

8

CN7

0.1 uF

, 4x

A

rray

GND

1

2

3

4

5

6

7

8

9

10

RN7

3.3K

O

h

m

, 8x

A

rray

GND

CLK_25

C

L

K

_25

1

2

3

U

10A

74L

V

C

32

9

10

8

U

10C

74L

V

C

32

VCC

14

GND

7

U

10E

74L

V

C

32

MA

C_

CS#

GND

GND

VCC_

+

3

.3

C5

1

0.1 uF

VCC_

+

3

.3

LED_CTRL0

LED_CTRL1

LED_CTRL2

1

2

3

4

5

6

7

8

S1

S2

L1

L2

L3

L4

J5

RJ4

5

7

8

9

10

11

12

13

14

15

16

17

18

TXD+

TXD-

TXD+

TXD-

RXD+

RXD+

RXD-

RXD-

T1

B

H

2006A

R1

9

49.9 O

h

m

, 1%

R2

0

49.9 O

h

m

, 1%

C2

6

0.1 uF

C2

7

0.1 uF

GND

GND

VCC_

P

HY1

VCC_

P

HY1

R1

7

R1

8

49.9 O

h

m

, 1%

C2

5

0.1 uF

C2

8

0.1 uF

GND

R28

75 O

h

m

, 1%

R27

C4

8

0.01 uF

, 2K

V

SHIELD

SHIELD

SHIELD

LED_

BU

F[

0

..

7

]

LED_

BU

F[

0

..

7

]

R29

R30

R31

R32

75 O

h

m

, 1%

FB3

FB4

FB5

FB6

F

B

E

A

D

, 68 O

h

m

@

100 M

H

z

AUX

_

P

O

W

E

R

0

AUX

_

P

O

W

E

R

1

AUX

_

P

O

W

E

R

2

AUX

_

P

O

W

E

R

3

A

U

X

_PO

W

E

R

[0..3]

AUX

_

P

O

W

E

R

[0

..

3

]

LED_BUF0

LED_BUF1

LED_BUF2

LED_BUF3

N

o

te

:

S

e

e

T

e

x

t

W

a

r

n

in

g

Wa

rn

ing:

F

ai

lur

e t

o

pr

ope

rl

y i

n

st

al

l a

n

d

c

onf

igur

e t

h

e a

ux. Et

he

rn

et

si

gna

ls

c

an

r

esul

t i

n

ve

ry

ba

d t

h

ings (

i.e

., f

ir

e, smoke

, ba

d ha

ir

da

ys)

.

I

f pow

er

i

s suppl

ie

d vi

a t

h

e RJ-

45 c

onne

ct

or

th

en

o

n

ly

th

e ferrite b

ead

s are in

st

alled

(n

o

t th

e

r

esi

st

or

s)

. I

f pow

er

i

s not

suppl

ie

d vi

a t

h

e RJ-

4

5

th

en

th

e res

is

to

rs

are in

st

alled

an

d

th

e b

ead

s are

not

.