CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

DS651UM21

©

Copyright 2004 Cirrus Logic, Inc.

43

Version 2.1

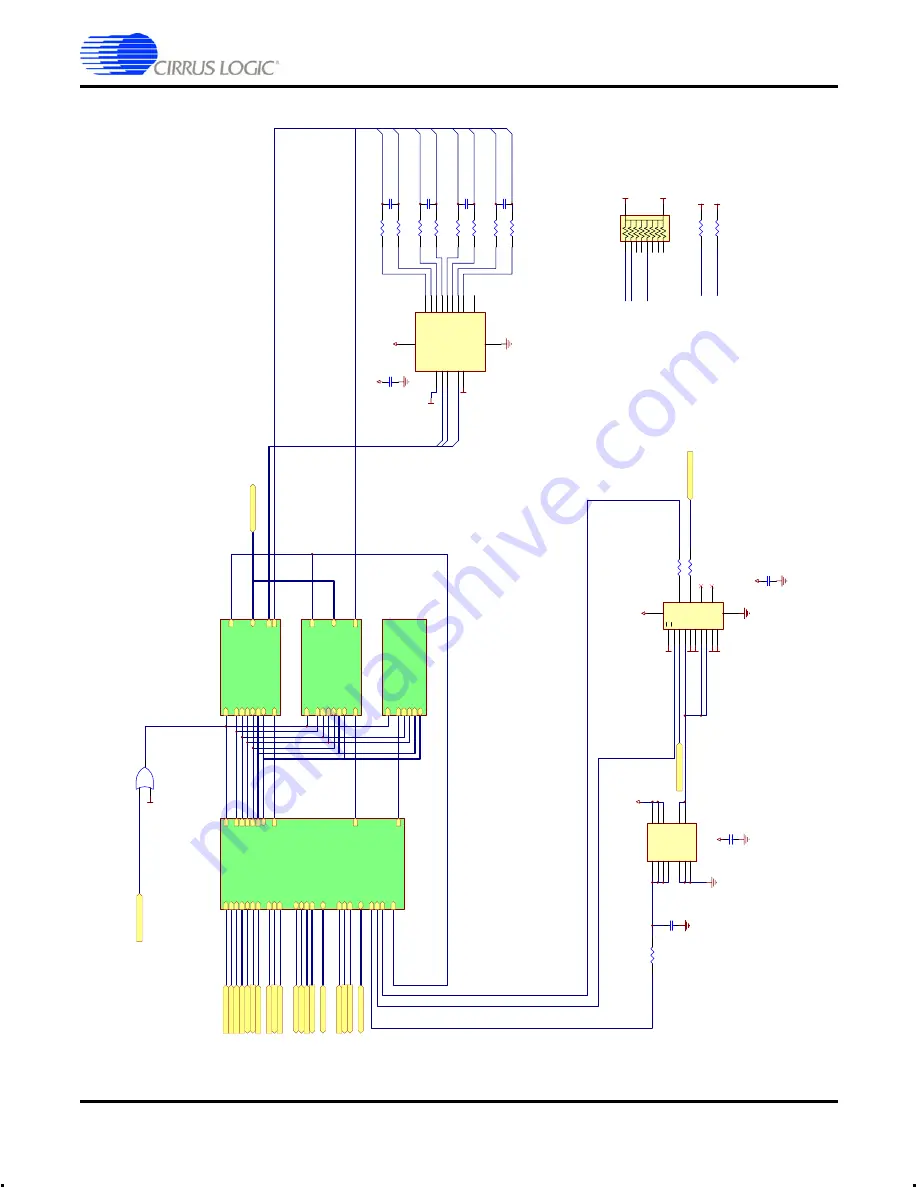

Figure 23. CM-2 RevE Schematic Page 2 of 7

CTRL

B1

GND

AB

2

OU

T

AB

3

VCC

B4

CTRL

A1

CTRL

C1

CTRL

D1

GND

C2

GND

D2

OU

T

CD3

VCC

A4

VCC

CD4

U3

24.576 M

H

z V

C

X

O

A/

B

1

1A

2

1B

3

1Y

4

2A

5

2B

6

2Y

7

GND

8

3Y

9

3B

10

3A

11

4Y

12

4B

13

4A

14

G

15

VCC

16

U4

74L

V

C

157

MCLK_

SEL

GND

HRESET_

BU

F#

MA

C_

CS#

OE#

WE#

IOWA

IT

A

DDR[

0

..

1

9

]

D

A

T

A

[0..15]

MA

C_

IRQ0

MA

C_

IRQ1

FLA

SH_

CS#

ADDR[0..19]

DATA[0..15]

AUX

_

P

O

W

E

R

[3

..

0

]

AUX

_

P

O

W

E

R

[3

..

0

]

U

A

R

T_

TX_

OE

UAR

T

_

R

X

D

U

A

R

T_

TXD

HRW

HDS#

HEN#

HREQ#

HA

CK#

HA

DDR[

0

..

3

]

HDA

TA

[0

..

7

]

FS1

SSI_

CLK

SSI_

DOU

T[

0

..

3

]

SSI_

DIN[

0

..

3

]

GP

IO[

0

..

1

]

HEN#

HRW

HDS#

HA

DDR[

0

..

3

]

HDA

TA

[0

..

7

]

HREQ#

HA

CK#

U

A

R

T_

TX_

OE

U

A

R

T_

TXD

UAR

T

_

R

X

D

FS1

SSI_

CLK

SSI_

DIN[

0

..

3

]

SSI_

DOU

T[

0

..

3

]

G

P

IO

[0..1]

HRESET#

D

A

T

A

[0..15]

A

DDR[

0

..

1

9

]

HRESET_

BU

F#

OE#

WE#

FLA

SH_

CS#

fl

ash

fl

ash.sc

h

REFCLK_

IN

WA

TCHDOG

MU

TE#

REFCLK_

IN

WA

TCHDOG

MU

TE#

R4

30.9 O

h

m

, 1%

R5

30.9 O

h

m

, 1%

C1

6

0.1 uF

R6

30.9 O

h

m

, 1%

R7

30.9 O

h

m

, 1%

C1

7

0.1 uF

R8

30.9 O

h

m

, 1%

R9

30.9 O

h

m

, 1%

C1

8

0.1 uF

R1

0

30.9 O

h

m

, 1%

R1

1

30.9 O

h

m

, 1%

C2

0

0.1 uF

L

E

D

F

ilters

g

o

clo

se

to

th

e c

o

n

n

ecto

r.

LED_

BU

F0

LED_

BU

F1

LED_

BU

F2

LED_

BU

F3

LED_

BU

F4

LED_

BU

F5

LED_

BU

F6

LED_

BU

F7

LED_BUF[0..7]

LED_CTRL[0..2]

LED_

CTRL0

LED_

CTRL1

LED_

CTRL2

GND

VCC_

+

3

.3

VCC_

+

3

.3

LED_

CTRL[

0

..

2

]

L

E

D

_B

U

F

[0..7]

LED_

BU

F[

0

..

7

]

MCLK_

IN

VCXO_

OU

T

VCXO_

OU

T

VCXO_

OU

T

GND

GND

GND

GND

MCLK_

INTERNA

L

MCLK_

OU

T

R1

6

24.9 O

h

m

, 1%

VCC_

+

3

.3

C1

9

0.1 uF

R1

2

3.3K

O

h

m

VCXO_

CTRL

MCLK_

IN

VCXO_

CTRL

MCLK_

SEL

MCLK_

INTERNA

L

MCLK_

OU

T

C2

1

0.1 uF

VCC_

+

3

.3

C2

2

0.1 uF

VCC_

+

3

.3

C1

5

0.1 uF

VCC_

+

3

.3

VCC_

+

3

.3

A

DDR[

0

..

1

9

]

D

A

T

A

[0..15]

AUX

_

P

O

W

E

R

[0

..

3

]

HRESET_

BU

F#

OE#

WE#

MA

C_

CS#

IOWA

IT

MA

C_

IRQ0

LED_

CTRL[

0

..

2

]

LED_

BU

F[

0

..

7

]

C

L

K

_25

m

ac

phy

1

m

ac

phy

1.sc

h

A

DDR[

0

..

1

9

]

D

A

T

A

[0..15]

AUX

_

P

O

W

E

R

[0

..

3

]

HRESET_

BU

F#

OE#

WE#

MA

C_

CS#

IOWA

IT

MA

C_

IRQ1

LED_

BU

F[

0

..

7

]

C

L

K

_25

m

ac

phy

2

m

ac

phy

2.sc

h

C

L

K

_25

C

L

K

_25

C

L

K

_25

R4

4

24.9 O

h

m

, 1%

Q1

1

Q2

2

Q3

3

Q4

4

Q5

5

Q6

6

Q7

7

GND

8

CA

SCA

DE

9

SCLR#

10

SCK

11

RCK

12

OE#

13

DIN

14

Q0

15

VCC

16

U2

74L

V

595

R3

10K

O

h

m

GND

WA

TCHDOG

MU

TE#

MCLK_

SEL

VCXO_

CTRL

R1

5

3.3K

O

h

m

GND

IOWA

IT

VCC_

+

3

.3

VCC_

+

3

.3

1

2

3

4

5

6

7

8

9

10

RN2

10K

O

h

m

, 8x

A

rray

4

5

6

U

10B

74L

V

C

32

GND

HRESET#

RSVD[

1

..

5

]

RSVD[

1

..

5

]

D

A

T

A

[0..15]

A

DDR[

0

..

1

9

]

HRESET_

BU

F#

OE#

WE#

FLA

SH_

CS#

MA

C_

CS#

IOWA

IT

U

A

R

T_

TX_

OE

UAR

T

_

R

X

D

U

A

R

T_

TXD

HRW

HDS#

HEN#

HREQ#

HA

CK#

HA

DDR[

0

..

3

]

HDA

TA

[0

..

7

]

MCLK_

INTERNA

L

FS1

SSI_

CLK

SSI_

DOU

T[

0

..

3

]

SSI_

DIN[

0

..

3

]

MCLK_

SEL

VCXO_

CTRL

MA

C_

IRQ0

MA

C_

IRQ1

GP

IO[

0

..

1

]

REFCLK_

IN

WA

TCHDOG

MU

TE#

C

L

K

_25

RSVD[

1

..

5

]

dsp

dsp.sc

h