44

©

Copyright 2004 Cirrus Logic, Inc.

DS651UM21

Version 2.1

CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

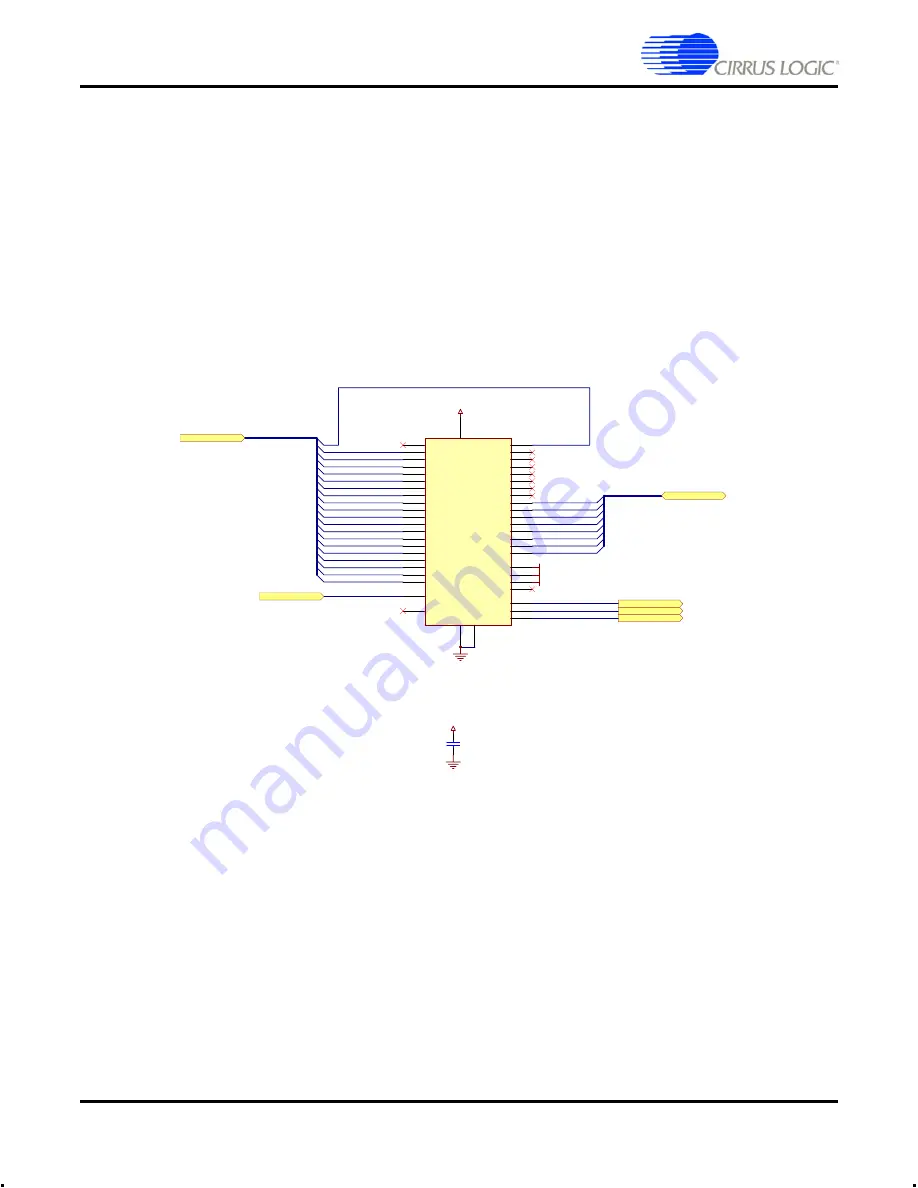

Figure 24. CM-2 RevE Schematic Page 3 of 7

A15

1

A14

2

A13

3

A12

4

A11

5

A10

6

A9

7

A8

8

NC/A19

9

NC

10

WE#

11

RESET#

12

NC/VPP

13

NC/WP#

14

NC/RY/BY#

15

NC/A18

16

A17

17

A7

18

A6

19

A5

20

A4

21

A3

22

A2

23

A1

24

A0

25

CE#

26

GND

27

OE#

28

D0

29

D8

30

D1

31

D9

32

D2

33

D10

34

D3

35

D11

36

VCC

37

D4

38

D12

39

D5

40

D13

41

D6

42

D14

43

D7

44

D15/A-1

45

GND

46

BYTE#

47

A16

48

U5

FLASH_TSOP

VCC_+3.3

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR[0..19]

DATA[0..15]

DATA[0..15]

ADDR[0..19]

HRESET_BUF#

HRESET_BUF#

OE#

WE#

FLASH_CS#

OE#

WE#

FLASH_CS#

C23

0.1 uF

VCC_+3.3

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

VCC_+3.3

VCC_+3.3

GND