CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

DS651UM21

©

Copyright 2004 Cirrus Logic, Inc.

45

Version 2.1

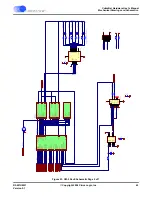

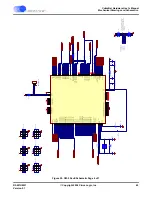

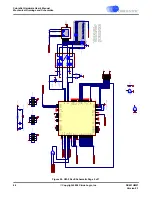

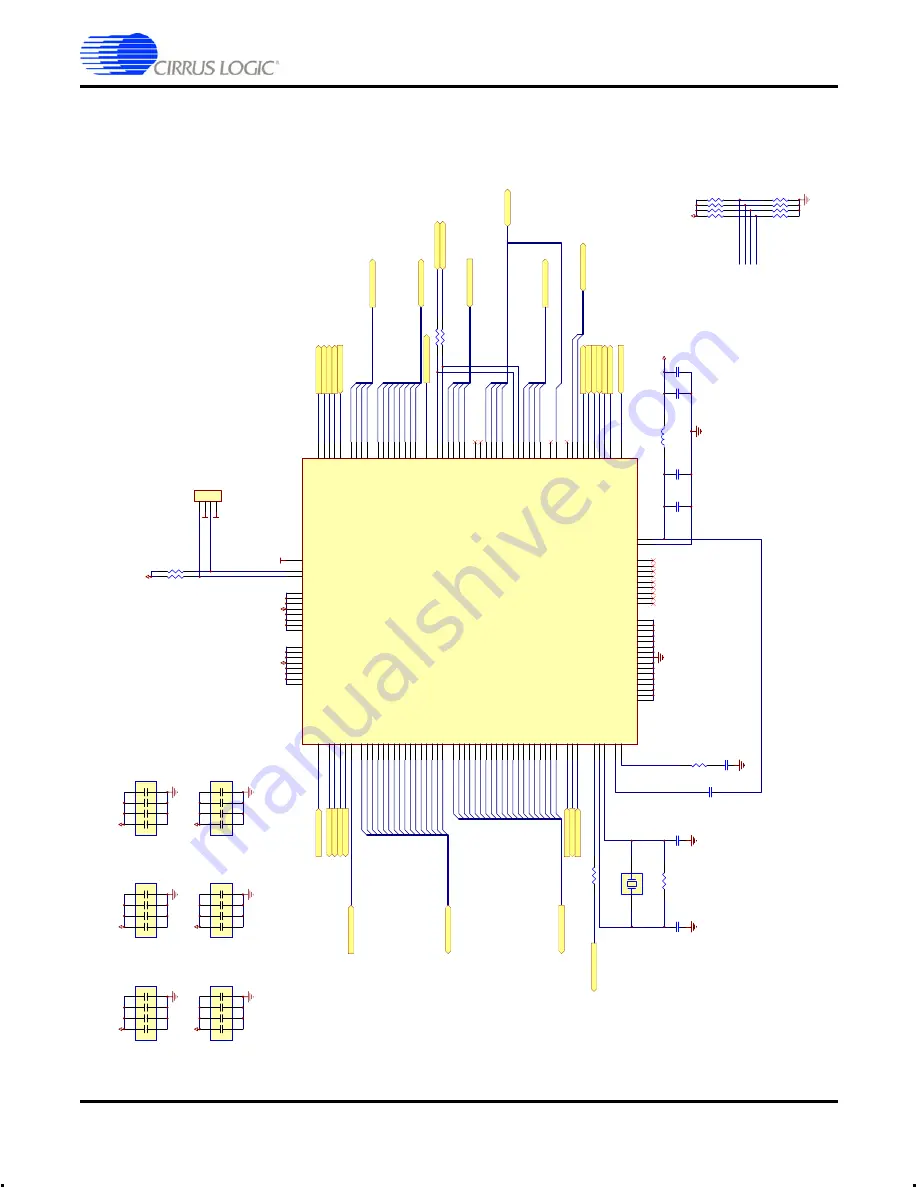

Figure 25. CM-2 RevE Schematic Page 4 of 7

VCXO_

CTRL

1

MCLK_

SEL

2

DBDA

3

DBCK

4

NC

5

NC

6

NC

7

DA

O_

MCLK

8

TEST

9

VDDD

10

HS3

11

NC

12

GND

13

NC

14

D

A

O

1

_

D

AT

A3

15

D

A

O

1

_

D

AT

A2

/H

S

2

16

D

A

O

1

_

D

AT

A1

/H

S

1

17

VDDIO

18

D

A

O

1

_

D

AT

A0

/H

S

0

19

DA

O1

_

S

CLK

20

GND

21

DA

O1

_

L

RCLK

22

U

A

R

T_

TX_

OE

23

VDDD

24

U

A

R

T_

TXD

25

UAR

T

_

R

X

D

26

GND

27

NC

28

VDDIO

33

GND

36

EXT_

WE#

38

VDDIO

44

GND

47

NC

50

NC

51

NC

52

NC

53

VDDD

54

S

D

_A

12/

E

X

T

_

A

1

1

55

S

D

_A

11/

E

X

T

_

A

1

0

56

GND

57

S

D

_A

9/

E

X

T

_

A

9

58

S

D

_A

8/

E

X

T

_

A

8

59

VDDIO

60

S

D

_A

7/

E

X

T

_

A

7

61

S

D

_A

6/

E

X

T

_

A

6

62

GND

63

S

D

_A

5/

E

X

T

_

A

5

64

EXT_

CS2

#

65

VDDD

66

S

D

_A

4/

E

X

T

_

A

4

67

S

D

_A

3/

E

X

T

_

A

3

68

GND

69

S

D

_A

2/

E

X

T

_

A

2

70

S

D

_A

1/

E

X

T

_

A

1

71

S

D

_A

0/

E

X

T

_

A

0

72

VDDIO

73

S

D

_A

10/

E

X

T

_

A

1

2

74

S

D

_A

14/

E

X

T

_

A

1

3

75

GND

76

S

D

_A

13/

E

X

T

_

A

1

4

77

NC

78

NC

79

NC

80

NC

81

EXT_

A

1

5

82

VDDD

83

EXT_

A

1

6

84

EXT_

A

1

7

85

GND

86

EXT_

A

1

8

87

EXT_

A

1

9

88

EXT_

OE#

89

EXT_

CS1

#

90

VDDIO

91

MU

TE#

92

RESET#

93

GND

94

WA

TCHDOG_

OU

T

95

IOWA

IT

96

REFCLK_

IN

97

VDDD

98

GP

IO0

99

GP

IO1

100

GND

101

HA

CK#

102

HDS#

103

HEN#

104

HA

DDR3

105

HA

DDR2

106

HR/W#

107

GP

IO2

108

HA

DDR1

109

HA

DDR0

110

HDA

TA

7

111

HDA

TA

6

112

VDDIO

113

HDA

TA

5

114

HDA

TA

4

115

GND

116

HDA

TA

3

117

HDA

TA

2

118

VDDD

119

HDA

TA

1

120

HDA

TA

0

121

GND

122

X

T

AL

_

O

UT

123

XTI

125

XTO

124

GND_A

126

FILT2

127

FILT1

128

VDD_A

129

VDDD

130

D

A

I1

_

D

AT

A3

131

D

A

I1

_

D

AT

A2

132

GND

133

D

A

I1

_

D

AT

A1

134

D

A

I1

_

D

AT

A0

135

VDDIO

136

D

A

I1_S

C

L

K

137

D

A

I1_L

R

C

L

K

138

GND

139

HREQ#

140

NC

141

NC

142

IRQ1

143

IRQ2

144

S

D

_D

7/

E

X

T

_

D

1

5

29

S

D

_D

6/

E

X

T

_

D

1

4

30

S

D

_D

5/

E

X

T

_

D

1

3

31

S

D

_D

4/

E

X

T

_

D

1

2

32

S

D

_D

3/

E

X

T

_

D

1

1

34

S

D

_D

2/

E

X

T

_

D

1

0

35

S

D

_D

1/

E

X

T

_

D

9

37

S

D

_D

0/

E

X

T

_

D

8

39

S

D

_D

15/

E

X

T

_

D

7

40

S

D

_D

14/

E

X

T

_

D

6

41

S

D

_D

13/

E

X

T

_

D

5

42

S

D

_D

12/

E

X

T

_

D

4

43

S

D

_D

11/

E

X

T

_

D

3

45

S

D

_D

10/

E

X

T

_

D

2

46

S

D

_D

9/

E

X

T

_

D

1

48

S

D

_D

8/

E

X

T

_

D

0

49

U6

C

S

18101

VCC_

+

1

.8

VCC_

+

3

.3

HRESET_

BU

F#

OE#

WE#

FLA

SH_

CS#

MA

C_

CS#

IOWA

IT

DA

TA

0

DA

TA

1

DA

TA

2

DA

TA

3

DA

TA

4

DA

TA

5

DA

TA

6

DA

TA

7

DA

TA

8

DA

TA

9

DA

TA

1

0

DA

TA

1

1

DA

TA

1

2

DA

TA

1

3

DA

TA

1

4

DA

TA

1

5

A

DDR0

A

DDR1

A

DDR2

A

DDR3

A

DDR4

A

DDR5

A

DDR6

A

DDR7

A

DDR8

A

DDR9

A

DDR1

0

A

DDR1

1

A

DDR1

2

A

DDR1

3

A

DDR1

4

A

DDR1

5

A

DDR1

6

A

DDR1

7

A

DDR1

8

A

DDR1

9

U

A

R

T_

TXD

UAR

T

_

R

X

D

U

A

R

T_

TX_

OE

HDA

TA

0

HDA

TA

1

HDA

TA

2

HDA

TA

3

HDA

TA

4

HDA

TA

5

HDA

TA

6

HDA

TA

7

HA

DDR0

HA

DDR1

HA

DDR2

HA

DDR3

HRW

HDS#

HREQ#

HA

CK#

HEN#

MCLK_

INTERNA

L

FS1

SSI_

CLK

SSI_

DIN0

SSI_

DIN1

SSI_

DIN2

SSI_

DIN3

SSI_

DOU

T0

SSI_

DOU

T1

SSI_

DOU

T2

SSI_

DOU

T3

RSVD1

RSVD2

RSVD4

RSVD3

VCXO_

CTRL

MA

C_

IRQ0

MA

C_

IRQ1

MCLK_

SEL

D

A

T

A

[0..15]

A

DDR[

0

..

1

9

]

HRESET_

BU

F#

OE#

WE#

FLA

SH_

CS#

MA

C_

CS#

IOWA

IT

C4

1

22 pF

C4

0

22 pF

SSI_

DOU

T[

0

..

3

]

SSI_

DIN[

0

..

3

]

HA

DDR[

0

..

3

]

HDA

TA

[0

..

7

]

D

A

T

A

[0..15]

A

DDR[

0

..

1

9

]

U

A

R

T_

TX_

OE

UAR

T

_

R

X

D

U

A

R

T_

TXD

HRW

HDS#

HEN#

HREQ#

HA

CK#

HA

DDR[

0

..

3

]

HDA

TA

[0

..

7

]

MCLK_

INTERNA

L

FS1

SSI_

CLK

SSI_

DOU

T[

0

..

3

]

SSI_

DIN[

0

..

3

]

MCLK_

SEL

VCXO_

CTRL

MA

C_

IRQ0

MA

C_

IRQ1

GP

IO0

GP

IO1

G

P

IO

[0..1]

G

P

IO

[0..1]

REFCLK_

IN

WA

TCHDOG

MU

TE#

REFCLK_

IN

WA

TCHDOG

MU

TE#

VCC_

+

3

.3

VCC_

+

1

.8

VCC_

+

1

.8

C2

4

0.1 uF

FB1

F

B

E

A

D

, 68 O

h

m

@

100 M

H

z

C4

10 uF

, X

5

R

, 6.3 V

o

lt

s

C5

10 uF

, X

5

R

, 6.3 V

o

lt

s

VCC_

DSP

A

R13

R14

3.3K

O

h

m

VCC_

+

3

.3

VCC_

+

3

.3

GND

DEBU

G_

CLK

DEBU

G_

DA

TA

D

ebug P

o

rt

RSVD1

SSI_

DOU

T0

SSI_

DOU

T1

SSI_

DOU

T2

HS0

- Down

HS1

- U

p

HS2

- Down

HS3

- Down

1

2

3

4

5

6

7

8

CN3

0.1 uF

, 4x

A

rray

1

2

3

4

5

6

7

8

CN2

0.1 uF

, 4x

A

rray

VCC_

+

3

.3

VCC_

+

1

.8

1

2

3

4

5

6

7

8

CN5

0.1 uF

, 4x

A

rray

1

2

3

4

5

6

7

8

CN4

0.1 uF

, 4x

A

rray

VCC_

+

1

.8

1

2

3

4

5

6

7

8

CN1

0.1 uF

, 4x

A

rray

GND

C4

3

1000 pF

, C

O

G

R4

1

5.90K

O

h

m

C4

2

2.2 uF

, X

7

R

, 1206

C

L

K

_25

C

L

K

_25

1

2

Y1

25 M

H

z

VCC_

+

3

.3

F

S

1_J

S

S

I_C

L

K

_J

C4

4

0.1 uF

R4

5

24.9 O

h

m

, 1%

VCC_

+

3

.3

1

2

3

4

5

6

7

8

CN1

2

0.1 uF

, 4x

A

rray

R5

3

R5

4

24.9 O

h

m

, 1%

F

S

1_J

S

S

I_C

L

K

_J

R43

R47

R49

R51

3.3K

O

h

m

R42

R46

R48

R50

3.3K

O

h

m

D

ef

aul

t B

o

o

t M

o

de

:

T

h

es

e pul

lups and pul

ld

o

w

ns are

use

d

to

se

t the

bo

o

t m

o

de

o

f the

D

S

P. T

h

e

ap

p

rop

ri

at

e r

es

is

tor

is

in

st

alled

t

o

s

elect

the

bo

o

t m

o

de

.

1

2

3

4

JP

1

CON4

R5

5

1 M

eg

O

hm

RSVD[

1

..

5

]

RSVD[

1

..

5

]

RSVD[

1

..

5

]

RSVD5