48

©

Copyright 2004 Cirrus Logic, Inc.

DS651UM21

Version 2.1

CobraNet Hardware User’s Manual

Mechanical Drawings and Schematics

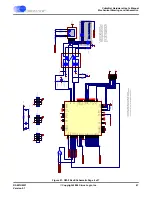

Figure 28. CM-2 RevE Schematic Page 7 of 7

HRESET#

GND

HEN#

GND

HRW

GND

HREQ#

GND

HA

CK#

GND

HDS#

GND

SSI_

CLK

SSI_

DOU

T0

GND

SSI_

DOU

T1

GND

SSI_

DOU

T2

GND

SSI_

DOU

T3

GND

SSI_

DIN0

GND

SSI_

DIN1

GND

SSI_

DIN2

GND

SSI_

DIN3

GND

FS1

GND

MCLK_

OU

T

GND

MCLK_

IN

GND

REFCLK_

IN

UAR

T

_

R

X

D

GND

U

A

R

T_

TXD

VCC_

+

3

.3

U

A

R

T_

TX_

OE

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

HDA

TA

0

VCC_

+

3

.3

HDA

TA

1

VCC_

+

3

.3

HDA

TA

2

VCC_

+

3

.3

HDA

TA

3

HDA

TA

4

VCC_

+

3

.3

HDA

TA

5

VCC_

+

3

.3

HDA

TA

6

VCC_

+

3

.3

HDA

TA

7

HRESET#

HA

DDR0

HEN#

HA

DDR1

HRW

HA

DDR2

HREQ#

HRESET#

HA

CK#

HA

CK#

HDS#

HDA

TA

[0

..

7

]

SSI_

CLK

HA

DDR[

0

..

3

]

SSI_

DOU

T0

SSI_

DOU

T1

SSI_

DOU

T2

SSI_

DOU

T3

SSI_

DIN0

SSI_

DIN1

SSI_

DIN2

SSI_

DIN3

FS1

MCLK_

OU

T

MCLK_

IN

REFCLK_

IN

UAR

T

_

R

X

D

U

A

R

T_

TXD

U

A

RT_

TX_

O

E

HA

DDR3

MU

TE#

VCC_

+

5

VCC_

+

5

HRW

HDS#

HEN#

HREQ#

HDA

TA

[0

..

7

]

HA

DDR[

0

..

3

]

SSI_

DOU

T[

0

..

3

]

SSI_

DIN[

0

..

3

]

HDA

TA

0

SSI_

DOU

T[

0

..

3

]

HDA

TA

1

SSI_

DIN[

0

..

3

]

HDA

TA

2

SSI_

CLK

HDA

TA

3

MCLK_

OU

T

HDA

TA

4

FS1

HDA

TA

5

U

A

R

T_

TXD

HDA

TA

6

UAR

T

_

R

X

D

HDA

TA

7

MCLK_

IN

HA

DDR0

REFCLK_

IN

HA

DDR1

U

A

R

T_

TX_

OE

HA

DDR2

VCC_

+

3

.3

C3

3

0.1 uF

C3

4

0.1 uF

C3

5

0.1 uF

C3

6

0.1 uF

C3

7

0.1 uF

C3

8

0.1 uF

VCC_

+

5

C3

9

0.1 uF

A

C

S

igna

l Re

tu

rn

P

at

h

Ca

ps

VCC_

+

3

.3

P

o

w

er

D

ec

oupl

ing C

aps

A

U

X_

P

OWER0

A

U

X_

P

OWER1

A

U

X_

P

OWER2

A

U

X_

P

OWER3

AUX

_

P

O

W

E

R

0

AUX

_

P

O

W

E

R

1

AUX

_

P

O

W

E

R

2

AUX

_

P

O

W

E

R

3

AUX

_

P

O

W

E

R

[0

..

3

]

AUX

_

P

O

W

E

R

[0

..

3

]

WA

TCHDOG

WA

TCHDOG

WA

TCHDOG

MU

TE#

MU

TE#

A1

A2

A3

A4

A5

A6

A7

A8

A9

A1

0

A1

1

A1

2

A1

3

A1

4

A1

5

A1

6

A1

7

A1

8

A1

9

A2

0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J3

CNM_

CONN4

0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A1

0

A1

1

A1

2

A1

3

A1

4

A1

5

A1

6

A1

7

A1

8

A1

9

A2

0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J1

CNM_

CONN4

0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A1

0

A1

1

A1

2

A1

3

A1

4

A1

5

A1

6

A1

7

A1

8

A1

9

A2

0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J4

CNM_

CONN4

0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A1

0

A1

1

A1

2

A1

3

A1

4

A1

5

A1

6

A1

7

A1

8

A1

9

A2

0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J2

CNM_

CONN4

0

N

o

te

: S

imi

la

r A

C

si

gna

l r

et

u

rn

pa

th

c

ap

s must

be

i

n

cl

ude

d on t

h

e mot

he

rboa

rd

ne

ar

t

h

e c

onne

ct

or

.

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

VCC_

+

3

.3

HRESET#

HEN#

HRW

HREQ#

HA

CK#

HDS#

SSI_

CLK

SSI_

DOU

T0

SSI_

DOU

T1

SSI_

DOU

T2

SSI_

DOU

T3

SSI_

DIN0

SSI_

DIN1

SSI_

DIN2

SSI_

DIN3

FS1

MCLK_

OU

T

MCLK_

IN

REFCLK_

IN

UAR

T

_

R

X

D

UAR

T

_

T

X

D

U

A

R

T_

TX_

OE

HA

DDR3

MU

TE#

VCC_

+

5

VCC_

+

5

HDA

TA

0

HDA

TA

1

HDA

TA

2

HDA

TA

3

HDA

TA

4

HDA

TA

5

HDA

TA

6

HDA

TA

7

HA

DDR0

HA

DDR1

HA

DDR2

AUX

_

P

O

W

E

R

0

AUX

_

P

O

W

E

R

1

AUX

_

P

O

W

E

R

2

AUX

_

P

O

W

E

R

3

WA

TCHDOG

1

M3

MOU

NTING

1

M4

MOU

NTING

1

M2

MOU

NTING

1

M1

MOU

NTING

R4

0

0 O

h

m

R3

9

0 O

h

m

Th

es

e t

w

o mou

n

tin

g h

o

les

a

re loca

te

d

a

t t

h

e

"

b

ac

k"

o

f the

C

M

-2

, ne

ar the

m

ai

n

i

n

te

rf

ac

e

con

n

ect

or

s.

T

h

es

e tw

o

m

o

unti

ng

ho

le

s are

l

o

ca

te

d ne

ar

the

f

ro

n

t pane

l o

f the

C

M

-2

.

C1

0

10 uF

, X

5

R

, 6.3 V

o

lt

s

C1

1

10 uF

, X

5

R

, 6.3 V

o

lt

s

C1

2

10 uF

, X

5

R

, 6.3 V

o

lt

s

C1

3

10 uF

, X

5

R

, 6.3 V

o

lt

s

C1

4

10 uF

, X

5

R

, 6.3 V

o

lt

s

RSVD3

RSVD3

RSVD1

RSVD2

RSVD4

RSVD1

RSVD2

RSVD4

HA

DDR3

HA

DDR0

HA

DDR1

HA

DDR2

HDA

TA

0

HDA

TA

1

HDA

TA

2

HDA

TA

3

HDA

TA

4

HDA

TA

5

HDA

TA

6

HDA

TA

7

HEN#

HDS#

HA

CK#

HREQ#

U

A

R

T_

TX_

OE

U

A

R

T_

TXD

UAR

T

_

R

X

D

REFCLK_

IN

GND

SSI_

DOU

T3

RSVD2

RSVD4

RSVD5

SSI_

DIN0

SSI_

DIN1

SSI_

DIN2

SSI_

DIN3

RSVD3

FS1

SSI_

CLK

N

o

te

: Pul

l-

ups/

do

w

ns o

n

S

S

I_D

O

U

T

[0..4] are

l

o

ca

te

d o

n

the

D

S

P sc

he

m

ati

c pag

e.

MCLK_

IN

Th

es

e p

u

llu

p

s/d

own

s a

re u

sed

t

o

a

ss

u

re

a

v

alid

logic lev

el if a

s

ign

al

is

tr

i-s

ta

te

d

or

n

o

t con

n

ect

ed

. In

s

o

me s

it

u

at

ion

s,

t

h

es

e ma

y n

o

t b

e r

equ

ir

ed

.

C5

0

0.01 uF

, 2K

V

SHIELD

P

lace near t

h

e Et

hernet

connect

ors

.

1

2

3

4

5

6

7

8

9

10

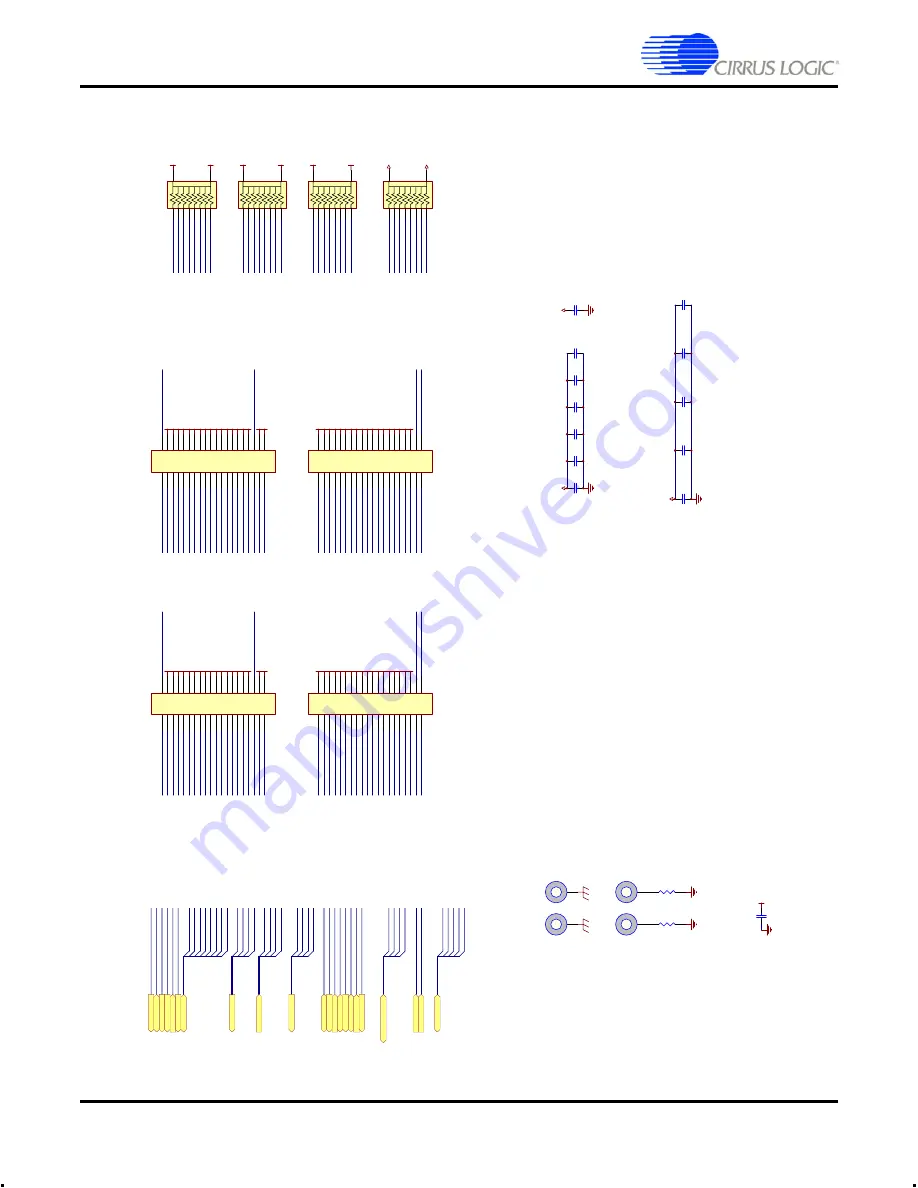

RN3

10K

O

h

m

, 8x

A

rray

1

2

3

4

5

6

7

8

9

10

RN4

10K

O

h

m

, 8x

A

rray

1

2

3

4

5

6

7

8

9

10

RN5

10K

O

h

m

, 8x

A

rray

1

2

3

4

5

6

7

8

9

10

RN6

10K

O

h

m

, 8x

A

rray

GND

GND

GND

GND

GND

VCC_

+

3

.3

VCC_

+

3

.3

HA

DDR3

RSVD[

1

..

5

]

RSVD[

1

..

5

]

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5